SLLS103E - DECEMBER 1990 - REVISED MARCH1997

- Meet or Exceed the Requirements of ANSI EIA/TIA-422-B and ITU Recommendation V.11

- Low Power, I<sub>CC</sub> = 100 μA Typ

- Operate From a Single 5-V Supply

- High Speed, t<sub>PLH</sub> = t<sub>PHL</sub> = 7 ns Typ

- Low Pulse Distortion, t<sub>sk(p)</sub> = 0.5 ns Typ

- High Output Impedance in Power-Off Conditions

- Improved Replacement for AM26LS31

#### description

The AM26C31C, AM26C31I, and AM26C31M are four complementary-output line drivers designed to meet the requirements of ANSI EIA/TIA-422-B and ITU (formerly CCITT). The 3-state outputs have high-current capability for driving balanced lines such as twisted-pair or parallel-wire transmission lines, and they provide the high-impedance state in the power-off condition. The enable function is common to all four drivers and offers the choice of an active-high or active-low enable input. BiCMOS circuitry reduces power consumption without sacrificing speed.

The AM26C31C is characterized for operation from 0°C to 70°C, the AM26C31I is characterized for operation from -40°C to 85°C, and the AM26C31M is characterized for operation from -55°C to 125°C

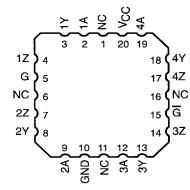

#### AM26C31C, AM26C31I . . . D OR DBT OR N PACKAGE AM26C31M . . . J OR W PACKAGE (TOP VIEW)

| 1A [<br>1Y [<br>1Z [<br>2Z [<br>2Y [ | 1<br>2<br>3<br>4<br>5<br>6<br>7 | O | 15<br>14<br>13<br>12<br>11 | ] 3Z           |

|--------------------------------------|---------------------------------|---|----------------------------|----------------|

| 2A [<br>GND [                        | 7<br>8                          |   | 10<br>9                    | 32<br>3Y<br>3A |

†The DB package is only available left-ended taped (order AM26C31IDBLE or AM26C31CDBLE).

### AM26C31M . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

## FUNCTION TABLE (each driver)

| INPUT | ENA | BLES | OUTPUTS |   |  |

|-------|-----|------|---------|---|--|

| Α     | G   | G    | Y       | Z |  |

| Н     | Н   | Х    | Н       | L |  |

| L     | Н   | Х    | L       | Н |  |

| Н     | X   | L    | н       | L |  |

| L     | X   | L    | L       | Н |  |

| Х     | L   | Н    | Z       | Ζ |  |

H = high level

X = irrelevant

L = low level

Z = high impedance (off)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright @ 1997, Texas Instruments Incorporated

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

■ 8961724 0108718 44T ■

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

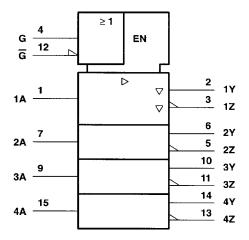

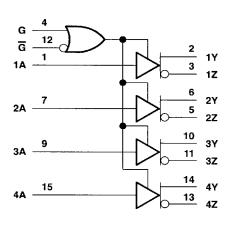

### logic symbol† logic diagram (positive logic)

NOTE A: The terminal numbers shown are for the D, DB, J, and W packages.

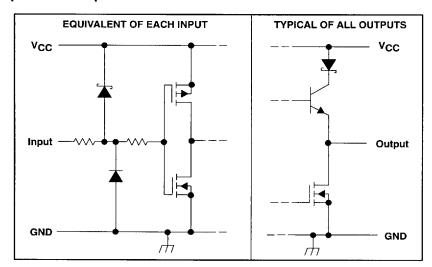

#### schematics of inputs and outputs

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)           | 0.5 V to 7 V                                                                                                         |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Input voltage range, V <sub>I</sub>                          | $\dots$ -0.5 V to V <sub>CC</sub> + 0.5 V                                                                            |

| Differential input voltage range, V <sub>ID</sub>            |                                                                                                                      |

| Output voltage range, VO                                     | $\dots \dots $ |

| Input or output clamp current, IIK or IOK                    | ±20 mA                                                                                                               |

| Output current, IO                                           | ±150 mA                                                                                                              |

| V <sub>CC</sub> current                                      | 200 mA                                                                                                               |

| GND current                                                  | –200 mA                                                                                                              |

| Continuous total power dissipation                           | See Dissipation Rating Table                                                                                         |

| Storage temperature range, T <sub>sto</sub>                  | 65 C to 150°C                                                                                                        |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                                                                                                                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values, except differential output voltage (VOD), are with respect to the network ground terminal.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|---------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------|

| D       | 950 mW                                | 7.6 mW/°C                                      | 608 mW                                | 494 mW                                | _                                      |

| DB      | 781 mW                                | 6.2 mW/°C                                      | 502 mW                                | 409 mW                                | _                                      |

| N       | 1150 mW                               | 9.2 mW/°C                                      | 736 mW                                | 598 mW                                | <del>-</del> .                         |

| FK      | 1375 mW                               | 11 mW/°C                                       | _                                     |                                       | 275 mW                                 |

| J       | 1375 mW                               | 11 mW/°C                                       | _                                     | _                                     | 275 mW                                 |

| w       | 1000 mW                               | 8.0 mW/°C                                      | _                                     | _                                     | 200 mW                                 |

#### recommended operating conditions

|                                             |          | <br>MIN | NOM | MAX | UNIT |

|---------------------------------------------|----------|---------|-----|-----|------|

| Supply voltage, V <sub>CC</sub>             |          | 4.5     | 5   | 5.5 | ٧    |

| Differential input voltage, V <sub>ID</sub> |          |         | ±7  |     | >    |

| High-level input voltage, VIH               |          | 2       |     |     | ٧    |

| Low-level input voltage, V <sub>IL</sub>    |          |         |     | 0.8 | ٧    |

| High-level output current, IOH              |          |         |     | -20 | mA   |

| Low-level output current, IOL               |          |         |     | 20  | mA   |

|                                             | AM26C31C | 0       |     | 70  |      |

| Operating free-air temperature, TA          | AM26C31I | -40     |     | 85  | °C   |

|                                             | AM26C31M | -55     |     | 125 |      |

■ 8961724 O108720 OT8 ■

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

## electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER           |                                                     | TEST CONDITIONS                   |                                  | AM26C31C<br>AM26C31I |      |       | UNIT |

|---------------------|-----------------------------------------------------|-----------------------------------|----------------------------------|----------------------|------|-------|------|

|                     |                                                     |                                   |                                  | MIN                  | TYPT | MAX   |      |

| VOH                 | High-level output voltage                           | I <sub>O</sub> = -20 mA           |                                  | 2.4                  | 3.4  |       | V    |

| $v_{OL}$            | Low-level output voltage                            | I <sub>O</sub> = 20 mA            |                                  |                      | 0.2  | 0.4   | V    |

| IVODI               | Differential output voltage magnitude               |                                   |                                  | 2                    | 3.1  |       | V    |

| ΔIV <sub>OD</sub> I | Change in magnitude of differential output voltage‡ |                                   |                                  |                      |      | ±0.4  | ٧    |

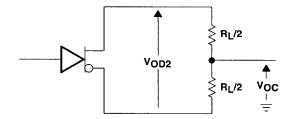

| Voc                 | Common-mode output voltage                          | $R_L = 100 \Omega$ ,              | See Figure 1                     |                      |      | 3     | V    |

| ΔIVOCI              | Change in magnitude of common-mode output voltage‡  | 1                                 |                                  |                      |      | ±0.4  | ٧    |

| lį                  | Input current                                       | $V_I = V_{CC}$ or (               | GND                              |                      |      | ±1    | μA   |

| la cm               | Driver output current with power off                | $V_{CC} = 0$ ,                    | V <sub>O</sub> = 6 V             |                      | _    | 100   |      |

| IO(off)             |                                                     | V <sub>CC</sub> = 0,              | V <sub>O</sub> = -0.25 V         |                      |      | 100   | μΑ   |

| los                 | Driver output short-circuit current                 | V <sub>O</sub> = 0                |                                  | -30                  |      | - 150 | mA   |

| 1                   | Link impodence off state output assumed             | V <sub>O</sub> = 2.5 V            |                                  |                      |      | 20    | μΑ   |

| loz                 | High-impedance off-state output current             | V <sub>O</sub> = 0.5 V            |                                  |                      |      | -20   | μΑ   |

|                     |                                                     | I <sub>O</sub> = 0,               | V <sub>1</sub> = 0 V or 5 V      |                      |      | 100   | μΑ   |

| ICC                 | Quiescent supply current                            | I <sub>O</sub> = 0,<br>See Note 2 | V <sub>I</sub> = 2.4 V or 0.5 V, |                      | 1.5  | 3     | mA   |

| CI                  | Input capacitance                                   |                                   |                                  |                      | 6    |       | pF   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

## switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER        |                                                          | TEST CO       | TEST CONDITIONS |     | AM26C31C<br>AM26C31I |     |      |

|------------------|----------------------------------------------------------|---------------|-----------------|-----|----------------------|-----|------|

|                  |                                                          |               |                 |     | TYP                  | MAX | UNIT |

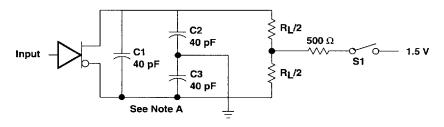

| <sup>t</sup> PLH | Propagation delay time, low- to high-level output        |               |                 | 5.7 | 7                    | 12  | ns   |

| <sup>t</sup> PHL | Propagation delay time, high- to low-level output        | S1 is open,   | See Figure 2    | 5.4 | 7                    | 12  | ns   |

| tsk(p)           | Pulse skew time (ItpLH - tpHLI)                          | 7             |                 | 0.5 | 4                    | ns  |      |

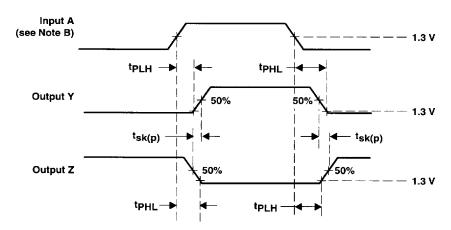

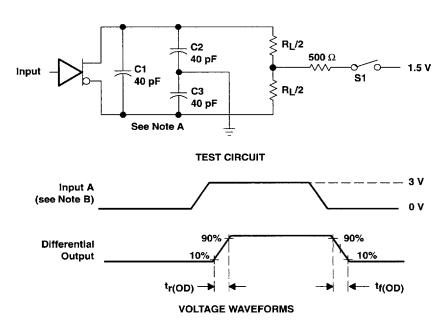

| tr(OD), tf(OD)   | Differential output rise and fall times                  | S1 is open,   | See Figure 3    |     | 5                    | 10  | ns   |

| <sup>t</sup> PZH | Output enable time to high level                         |               |                 |     | 10                   | 19  | ns   |

| <sup>t</sup> PZL | Output enable time to low level                          | 7             | 0 5             |     | 10                   | 19  | ns   |

| <sup>t</sup> PHZ | Output disable time from high level                      | S1 is closed, | See Figure 4    |     | 7                    | 16  | ns   |

| <sup>t</sup> PLZ | Output disable time from low level                       | 7             |                 |     | 7                    | 16  | ns   |

| C <sub>pd</sub>  | Power dissipation capacitance (each driver) (see Note 3) | S1 is open,   | See Figure 2    |     | 170                  |     | pF   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5$  V and  $T_A = 25$ °C.

<sup>‡</sup> ΔIVODI and ΔIVOCI are the changes in magnitude of VOD and VOC, respectively, that occur when the input is changed from a high level to a low level.

NOTE 2: This parameter is measured per input. All other inputs are at 0 or 5 V.

NOTE 3: Cpd is used to estimate the switching losses according to Pp = Cpd VCC<sup>2</sup> f, where f is the switching frequency.

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

#### electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                     | PARAMETER                                           |                                       | TEST CONDITIONS                          |            | AM26C31M |      |      |      |

|---------------------|-----------------------------------------------------|---------------------------------------|------------------------------------------|------------|----------|------|------|------|

| ļ                   | PARAMETER                                           |                                       | 1231 CONDITIONS                          |            | MIN      | TYPT | MAX  | TINU |

| VOH                 | High-level output voltage                           | $I_{O} = -20 \text{ mA}$              |                                          |            | 2.2      | 3.4  |      | ٧    |

| VOL                 | Low-level output voltage                            | IO = 20 mA                            |                                          |            |          | 0.2  | 0.4  | ٧    |

| IV <sub>OD</sub> I  | Differential output voltage magnitude               |                                       |                                          |            | 2        | 3.1  |      | ٧    |

| ΔIV <sub>OD</sub> I | Change in magnitude of differential output voltage‡ | D 400 C                               | 0 5: 1                                   |            | :        |      | ±0.4 | ٧    |

| Voc                 | Common-mode output voltage                          | $R_L$ = 100 Ω, See Figure 1           |                                          |            |          |      | 3    | ٧    |

| ΔIVOCI              | Change in magnitude of common-mode output voltage‡  |                                       |                                          |            |          |      | ±0.4 | ٧    |

| l I <sub>I</sub>    | Input current                                       | V <sub>I</sub> = V <sub>CC</sub> or 0 | V <sub>I</sub> = V <sub>CC</sub> or GND  |            |          |      | ±1   | μА   |

| la ( m              | Driver output current with power off                | $V_{CC} = 0$ ,                        | V <sub>O</sub> = 6 V                     |            |          |      | 100  | ^    |

| <sup>I</sup> O(off) | Driver datput current with power on                 | $V_{CC} = 0$ ,                        | V <sub>O</sub> = −0.25 V                 |            |          |      | -100 | μА   |

| los                 | Driver output short-circuit current                 | V <sub>O</sub> = 0                    |                                          |            |          |      | -170 | mA   |

| lon                 | High-impedance off-state output current             | $V_0 = 2.5 \text{ V}$                 |                                          |            |          |      | 20   | μΑ   |

| loz                 | High-impedance oil-state output current             | V <sub>O</sub> = 0.5 V                |                                          |            |          |      | -20  | μΑ   |

| laa                 | Quiescent august ourrent                            | l <sub>O</sub> = 0,                   | $V_I = 0 V \text{ or } 5 V$              |            |          |      | 100  | μΑ   |

| Icc                 | Quiescent supply current                            | IO = 0,                               | $V_I = 2.4 \text{ V or } 0.5 \text{ V},$ | See Note 2 |          |      | 3.2  | mA   |

| CI                  | Input capacitance                                   |                                       |                                          |            |          | 6    |      | pF   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

## switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER          |                                                          | TEST C        | TEST CONDITIONS |     | AM26C31M |     |      |

|--------------------|----------------------------------------------------------|---------------|-----------------|-----|----------|-----|------|

|                    | PANAMETER                                                | TEST CO       | DINDITIONS      | MIN | TYP†     | MAX | UNIT |

| tPLH               | Propagation delay time, low- to high-level output        |               |                 |     | 7        | 12  | ns   |

| tPHL               | Propagation delay time, high- to low-level output        | S1 is open,   | See Figure 2    |     | 6.5      | 12  | ns   |

| t <sub>sk(p)</sub> | Pulse skew time (ItpLH - tpHLI)                          | 7             |                 |     | 0.5      | 4   | ns   |

| tr(OD), tf(OD)     | Differential output rise and fall times                  | S1 is open,   | See Figure 3    |     | 5        | 12  | ns   |

| <sup>t</sup> PZH   | Output enable time to high level                         |               |                 |     | 10       | 19  | ns   |

| tPZL               | Output enable time to low level                          | S1 is closed, | See Figure 4    |     | 10       | 19  | ns   |

| <sup>t</sup> PHZ   | Output disable time from high level                      | 31 is closed, | See Figure 4    |     | 7        | 16  | ns   |

| <sup>t</sup> PLZ   | Output disable time from low level                       |               |                 |     | 7        | 16  | ns   |

| C <sub>pd</sub>    | Power dissipation capacitance (each driver) (see Note 3) | S1 is open,   | See Figure 2    |     | 100      |     | pF   |

† All typical values are at  $V_{CC}$  = 5 V and  $T_A$  = 25°C. NOTE 3:  $C_{pd}$  is used to estimate the switching losses according to  $P_D = C_{pd} \times V_{CC}^2$  f, where f is the switching frequency.

8961724 0108722 970 🚥

<sup>\$\(\</sup>delta\IV\_{OD}\) and \(\Delta\IV\_{OC}\) are the changes in magnitude of V\_{OD} and V\_{OC}, respectively, that occur when the input is changed from a high level to a low level.

NOTE 2: This parameter is measured per input. All other inputs are at 0 V or 5 V.

#### PARAMETER MEASUREMENT INFORMATION

Figure 1. Differential and Common-Mode Output Voltages

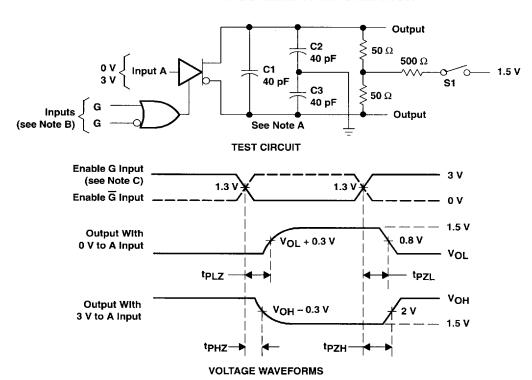

#### **TEST CIRCUIT**

NOTES: A. C1 – C3 includes probe and jig capacitance.

B. All input pulses are supplied by generators having the following characteristics: PRR ≤ 1 MHz, duty cycle ≤ 50%, and t<sub>f</sub> t<sub>f</sub> ≤ 6 ns.

Figure 2. Propagation Delay Time and Skew Waveforms and Test Circuit

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

**■** 8961724 0108723 807 **■**

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. C1 - C3 includes probe and jig capacitance.

B. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz, duty cycle  $\leq$  50%, and  $t_r$ ,  $t_f \leq$  6 ns.

Figure 3. Differential Output Rise and Fall Time Waveforms and Test Circuit

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A. C1 – C3 includes probe and jig capacitance.

- B. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz, duty cycle  $\leq$  50%, t<sub>r</sub> < 6 ns, and t<sub>f</sub> < 6 ns.

- C. Each enable is tested separately.

Figure 4. Output Enable and Disable Time Waveforms and Test Circuit

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

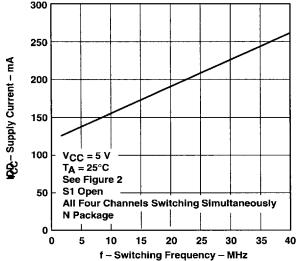

#### TYPICAL CHARACTERISTICS

## **SUPPLY CURRENT SWITCHING FREQUENCY** 300 250

Figure 5

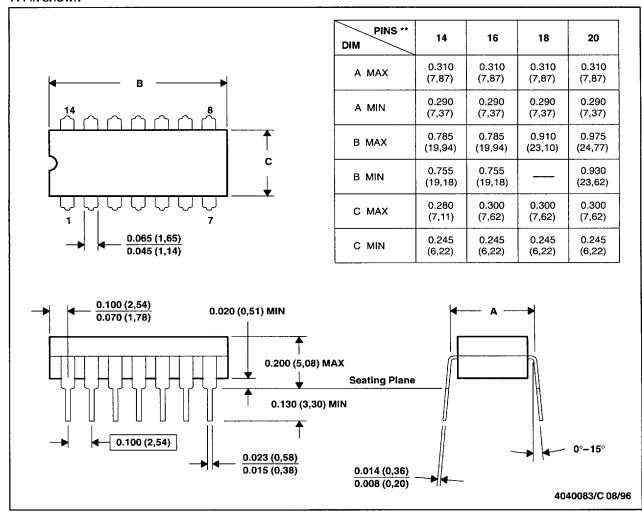

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

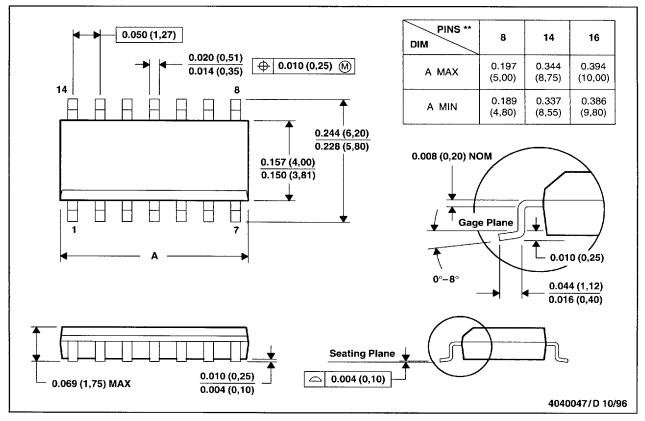

#### **MECHANICAL INFORMATION**

#### D (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### 14 PIN SHOWN

NOTES: D. All linear dimensions are in inches (millimeters).

E. This drawing is subject to change without notice.

F. Body dimensions do not include mold flash or protrusion, not to exceed 0.006 (0,15).

G. Falls within JEDEC MS-012

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

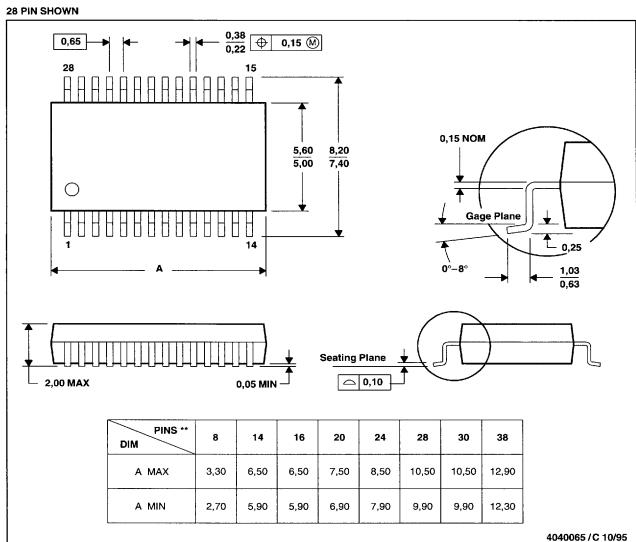

#### **MECHANICAL INFORMATION**

### DB (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-150

8961724 0108728 399

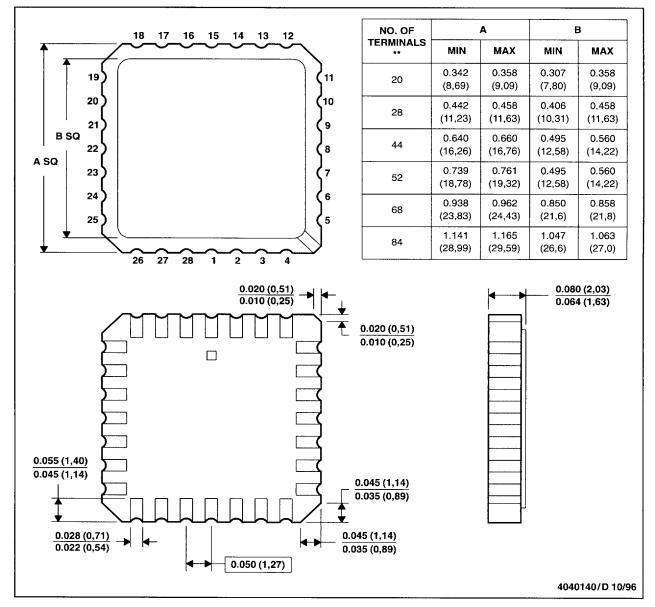

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

#### MECHANICAL INFORMATION

#### FK (S-CQCC-N\*\*)

**28 TERMINAL SHOWN**

#### **LEADLESS CERAMIC CHIP CARRIER**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a metal lid.

- D. The terminals are gold plated.

- E. Falls within JEDEC MS-004

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

8961724 0108729 225 📟

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

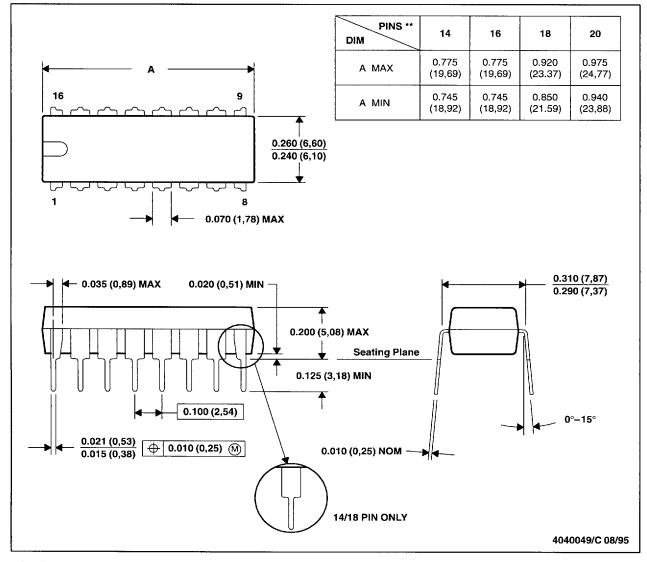

#### **MECHANICAL INFORMATION**

### J (R-GDIP-T\*\*)

#### 14 PIN SHOWN

#### **CERAMIC DUAL-IN-LINE PACKAGE**

- NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL-STD-1835 GDIP1-T14, GDIP1-T16, GDIP1-T18, and GDIP1-T20

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

#### **MECHANICAL INFORMATION**

#### N (R-PDIP-T\*\*)

#### PLASTIC DUAL-IN-LINE PACKAGE

#### 16 PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-001 (20 pin package is shorter then MS-001.)

SLLS103E - DECEMBER 1990 - REVISED MARCH1997

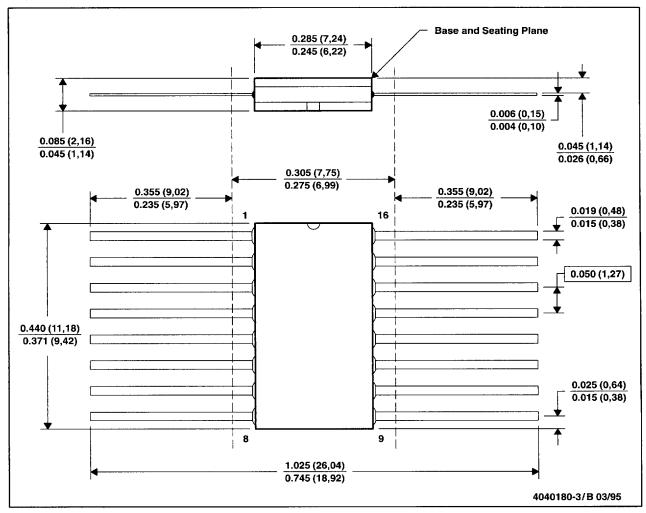

#### **MECHANICAL INFORMATION**

#### W (R-GDFP-F16)

#### **CERAMIC DUAL FLATPACK**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only.

- E. Falls within MIL-STD-1835 GDFP1-F16 and JEDEC MO-092AC

#### IMPORTANT NOTICE

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

8961724 0108733 756

77933