### 80C575/83C575/87C575

#### **DESCRIPTION**

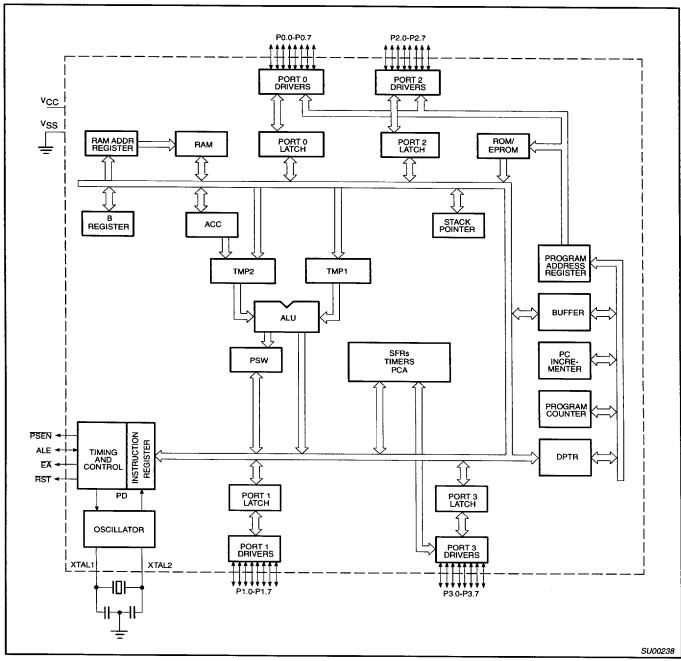

The Philips 80C575/83C575/87C575 is a high-performance microcontroller fabricated with Philips high-density CMOS technology. The Philips CMOS technology combines the high speed and density characteristics of HMOS with the low power attributes of CMOS. Philips epitaxial substrate minimizes latch-up sensitivity.

The 8XC575 contains an 8k × 8 ROM (83C575) EPROM (87C575), a 256 × 8 RAM, 32 I/O lines, three 16-bit counter/timers, a Programmable Counter Array (PCA), a seven-source, two-priority level nested interrupt structure, an enhanced UART, four analog comparators, power-fail detect and oscillator fail detect circuits, and on-chip oscillator and clock circuits.

In addition, the 8XC575 has a low active reset, and the port pins are reset to a low level. There is also a fully configurable watchdog timer, and internal power on clear circuit. The part includes idle mode and power-down mode states for reduced power consumption.

#### **FEATURES**

- 80C51 based architecture

- 8k × 8 ROM (83C575)

- 8k × 8 EPROM (87C575)

- ROMIess (80C575)

- 256 × 8 RAM

- Three 16-bit counter/timers

- Programmable Counter Array

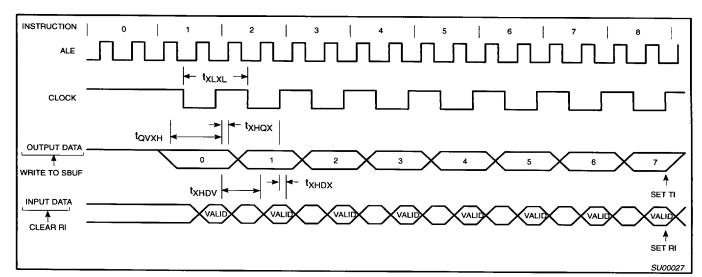

- Enhanced UART

- Boolean processor

- Oscillator fail detect

- Low active reset

- Asynchronous low port reset

- Schmitt trigger inputs

- 4 analog comparators

- Watchdog timer

- Low V<sub>CC</sub> detect

- Memory addressing capability

- 64k ROM and 64k RAM

- Power control modes:

- Idle mode

- Power-down mode

- CMOS and TTL compatible

- 4.0 to 16MHz

- Extended temperature ranges

- OTP package available

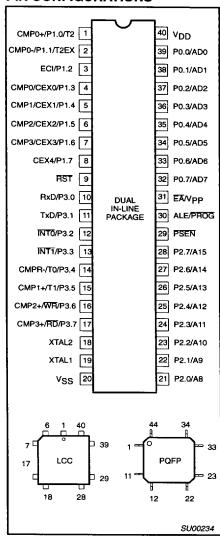

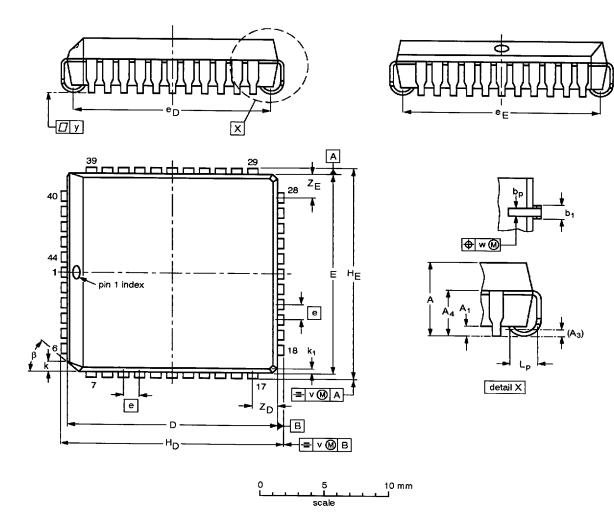

#### PIN CONFIGURATIONS

#### ORDERING INFORMATION

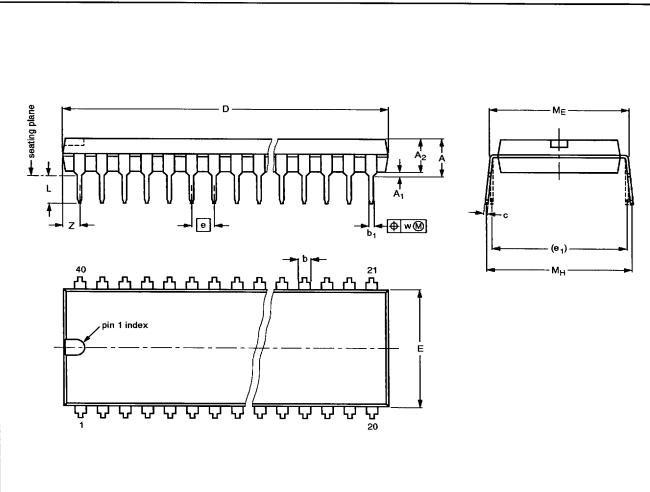

| ROMiess     | ROMIess ROM EPROM <sup>1</sup> |              |     | TEMPERATURE RANGE °C AND PACKAGE                 | FREQ<br>(MHz) | DRAWING<br>NUMBER |  |

|-------------|--------------------------------|--------------|-----|--------------------------------------------------|---------------|-------------------|--|

| P80C575EBPN | P83C575EBPN                    | P87C575EBPN  | OTP | 0 to +70, 40-Pin Plastic Dual In-line Package    | 16            | SOT129-1          |  |

| P80C575EBAA | P83C575EBAA                    | P87C575EBAA  | OTP | 0 to +70, 44-Pin Plastic Leaded Chip Carrier     | 16            | SOT187-2          |  |

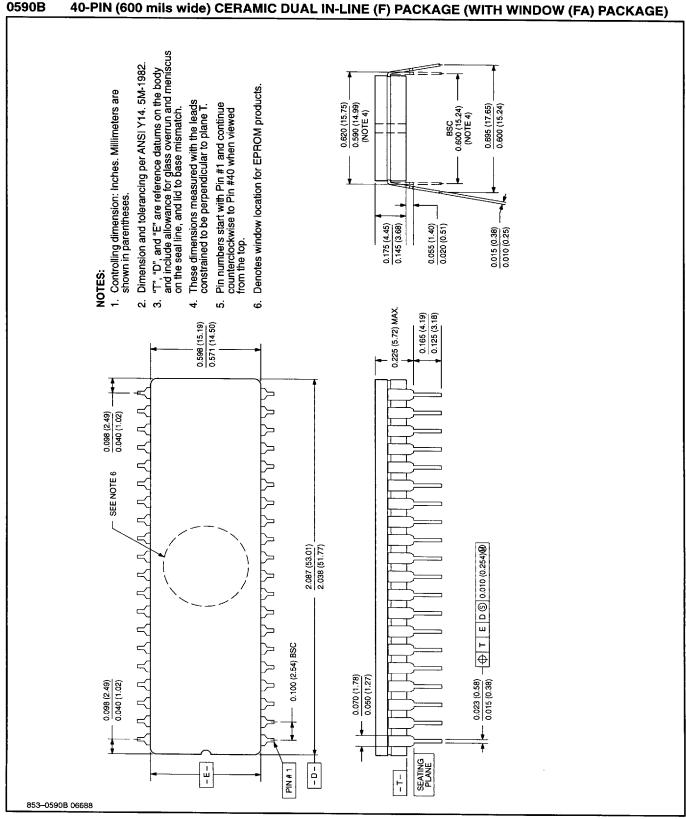

|             |                                | P87C575EBFFA | UV  | 0 to +70, 40-Pin Ceramic Dual In-line Package    | 16            | 0590B             |  |

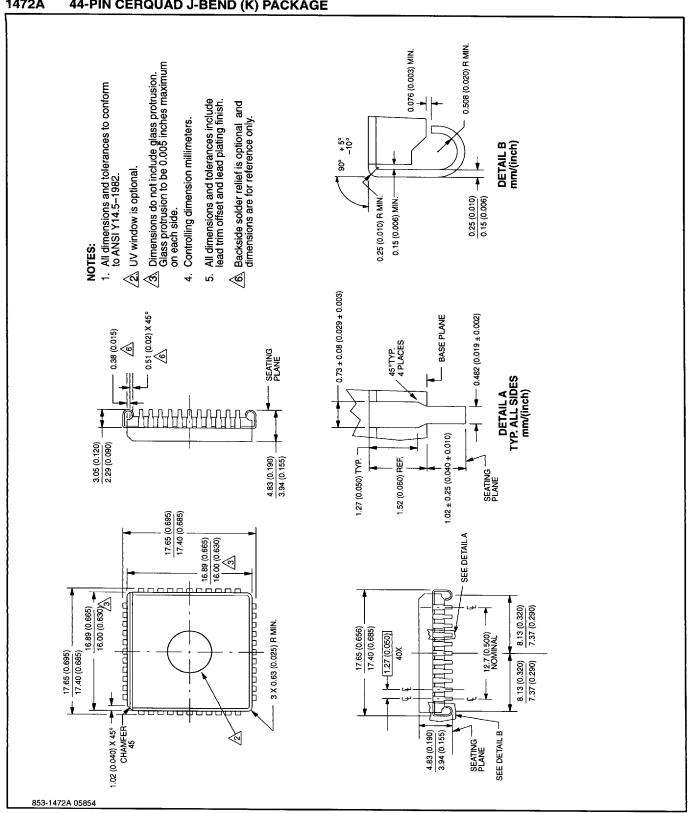

|             |                                | P87C575EBLKA | UV  | 0 to +70, 44-Pin Ceramic Leaded Chip Carrier     | 16            | 1472A             |  |

| P80C575EHPN | P83C575EHPN                    | P87C575EHPN  | OTP | -40 to +125, 40-Pin Plastic Dual In-line Package | 16            | SOT129-1          |  |

| P80C575EHAA | P83C575EHAA                    | P87C575EHAA  | OTP | -40 to +125, 44-Pin Plastic Leaded Chip Carrier  | 16            | SOT187-2          |  |

|             |                                | P87C575EHFFA | UV  | -40 to +125, 40-Pin Ceramic Dual In-line Package | 16            | 0590B             |  |

| P80C575EBBB | P83C575EBBB                    | P87C575EBBB  | OTP | 0 to +70, 44-Pin Plastic Quad Flat Pack          | 16            | SOT307-2          |  |

#### NOTE:

1. OTP - One Time Programmable EPROM. UV - Erasable EPROM

7110826 0107660 T7T **....**

2

1996 Aug 16

853-1684 17188

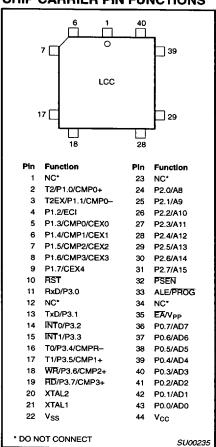

# CERAMIC AND PLASTIC LEADED CHIP CARRIER PIN FUNCTIONS

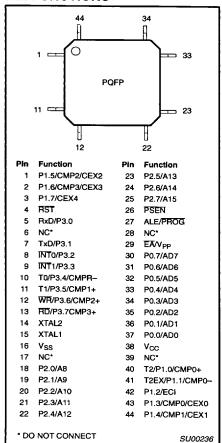

# PLASTIC QUAD FLAT PACK PIN FUNCTIONS

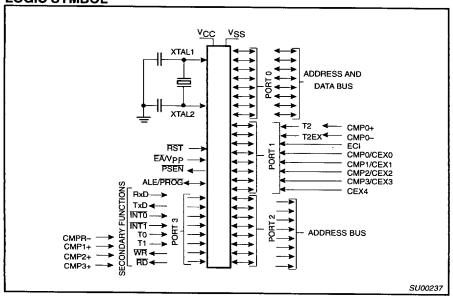

#### LOGIC SYMBOL

1996 Aug 16

**7110826 0107661 906**

#### **BLOCK DIAGRAM**

# 80C575/83C575/87C575

#### **PIN DESCRIPTIONS**

|                 | PIN   | NUMB         | ER           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-----------------|-------|--------------|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MNEMONIC        | DIP   | LCC          | QFP          | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| V <sub>SS</sub> | 20    | 22           | 16           | 1    | Ground: 0V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| V <sub>CC</sub> | 40    | 44           | 38           | ı    | Power Supply: This is the power supply voltage for normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

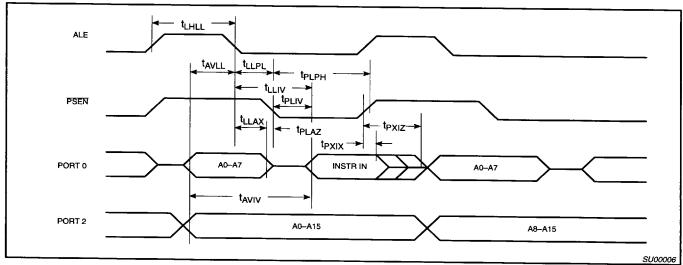

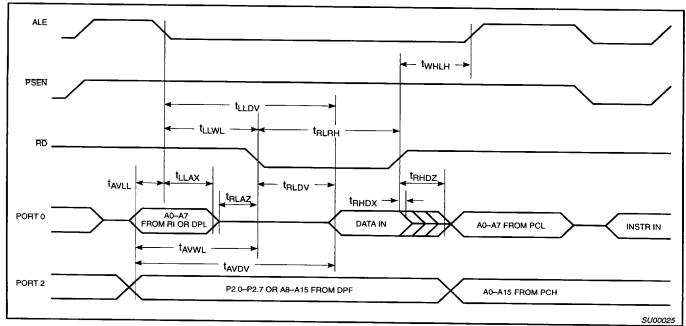

| P0.0-0.7        | 39-32 | 43-36        | 37-30        | I/O  | Port 0: Port 0 is an open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s. Port 0 also receives code bytes during EPROM programming and outputs code bytes during program verification. External pull-ups are required during program verification. During reset, port 0 will be asynchronously driven low and will remain low until written to by software. All port 0 pins have Schmitt trigger inputs with 200mV hysteresis. A weak pulldown on port 0 guarantees positive leakage current (see DC Electrical Characteristics: I <sub>L1</sub> ).                                                               |  |  |  |  |  |

| P1.0-P1.7       | 1-8   | 2-9          | 40-44<br>1-3 | I/O  | Port 1: Port 1 is an 8-bit bidirectional I/O port. Port 1 pins have internal pull-ups such that pins that have 1s written to them can be used as inputs but will source current when externally pulled low (see DC Electrical Characteristics: I <sub>IL</sub> ). Port 1 receives the low-order address byte during program memory verification and EPROM programming. During reset, port 1 will be asynchronously driven low and will remain low until written to by software. All port 1 pins have Schmitt trigger inputs with 50mV hysteresis. Port 1 pins also serve alternate functions as follows:                                                                                                                                                                                                                                                                            |  |  |  |  |  |

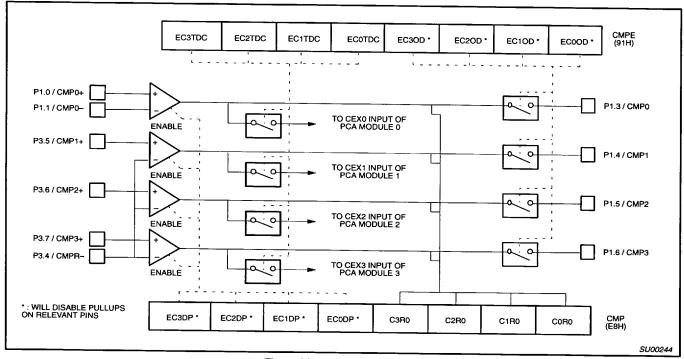

|                 | 1     | 2            | 40           | 1/0  | P1.0 T2 Timer 2 external I/O – clockout (programmable) CMP0+ Comparator 0 positive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                 | 2     | 3            | 41           | ۱ ا  | P1.1 T2EX Timer 2 capture input CMP0- Comparator 0 negative input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| [               | 3     | 4            | 42           | 1    | P1.2 ECI PCA count input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                 | 4     | 5            | 43           | 1/0  | P1.3 CEX0 PCA module 0 external I/O CMP0 Comparator 0 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 1               | 5     | 6            | 44           | 1/0  | P1.4 CEX1 PCA module 1 external I/O CMP1 Comparator 1 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                 | 6     | 7            | 1            | 1/0  | P1.5 CEX2 PCA module 2 external I/O CMP2 Comparator 2 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                 | 7     | 8            | 2            | 1/0  | P1.6 CEX3 PCA module 3 external I/O CMP3 Comparator 3 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                 | 8     | 9            | 3            | 1/0  | P1.7 CEX4 PCA module 4 external I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| P2.0-P2.7       | 21-28 | 24-31        | 18-25        | I/O  | Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them can be used as inputs, but will source current when externally pulled low (see DC Electrical Characteristics: I <sub>IL</sub> ). Port 2 emits the high-order address byte during accesses to external program and data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. Port 2 receives the high-order address byte during program verification and EPROM programming. During reset, port 2 will be asynchronously driven low and will remain low until written to by software. Port 2 can be made open drain by writing to the P2OD register (AIH). In open drain mode, weak pulldowns on port 2 guarantee positive leakage current (see DC Electrical Characteristics I <sub>L1</sub> ). |  |  |  |  |  |

| P3.0-P3.7       | 10-17 | 11,<br>13-19 | 5,<br>7-13   | I/O  | Port 3: Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins except P3.1 that have 1s written to them can be used as inputs but will source current when externally pulled low (see DC Electrical Characteristics: $I_{\rm IL}$ ). P3.1 will be a high impedance pin except while transmitting serial data, in which case the strong pull-up will remain on continuously when outputting a 1 level. The P3.1 output drive level when transmitting can be set to one of two levels by the writing to the P3.1 register bit. During reset all pins (except P3.1) will be asynchronously driven low and will remain low until written to by software. All port 3 pins have Schmitt trigger inputs with 200mV hysteresis, except P3.2 and P3.3, which have 50mV hysteresis. Port 3 pins serve alternate functions as follows:                                  |  |  |  |  |  |

# 80C575/83C575/87C575

### PIN DESCRIPTIONS (Continued)

|                    | PIN | NUMBI | ER  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|-----|-------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC           | DIP | LCC   | QFP | TYPE   | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    |     |       |     |        | Port 3: (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| j l                | 10  | 11    | 5   | 1      | P3.0 RxD Serial receive port                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                    | 11  | 13    | 7   | 0      | P3.1 TxD Serial transmit port enabled only when transmitting serial data                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                    | 12  | 14    | 8   |        | P3.2 INTO External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | 13  | 15    | 9   | 1      | P3.3 INT1 External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | 14  | 16    | 10  |        | P3.4 T0 Timer/counter 0 input CMPR- Common - reference to comparators 1, 2, 3                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    | 15  | 17    | 11  | 1      | P3.5 T1 Timer/counter 1 input CMP1+ Comparator 1 positive input                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | 16  | 18    | 12  | 0      | P3.6 WR External data memory write strobe CMP2+ Comparator 2 positive input                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    | 17  | 19    | 13  | 0      | P3.7 RD External data memory read strobe CMP3+ Comparator 3 positive input                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RST                | 9   | 10    | 4   | l      | <b>Reset:</b> A low on this pin asynchronously resets all port pins to a low state except P3.1. The pin must be held low with the oscillator running for 24 oscillator cycles to initialize the internal registers. An internal diffused resistor to $V_{\rm CC}$ permits a power on reset using only an external capacitor to $V_{\rm SS}$ . RST has a Schmitt trigger input stage to provide additional noise immunity with a slow rising input voltage.                                           |

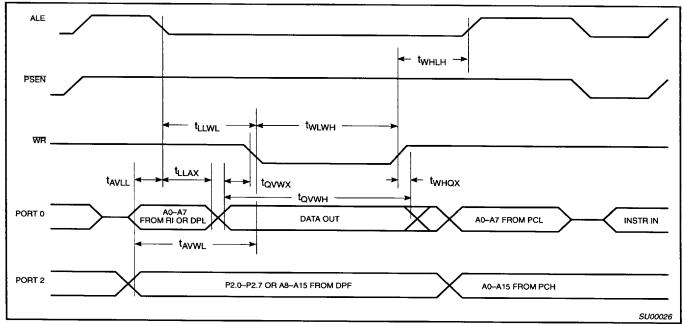

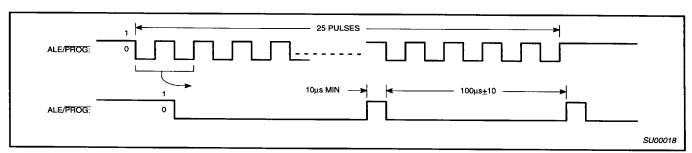

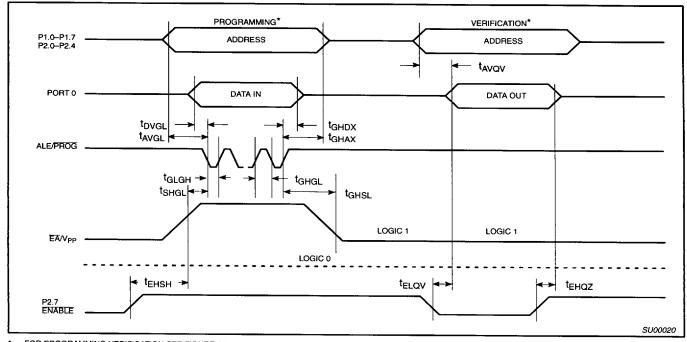

| ALE/PROG           | 30  | 33    | 27  | I/O    | Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. ALE is switched off if the bit 0 in the AUXR register (8EH) is set. This pin is also the program pulse input (PROG) during EPROM programming. |

| PSEN               | 29  | 32    | 26  | 0      | Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                                                                        |

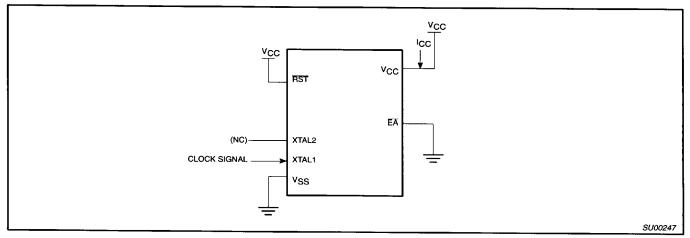

| EA/V <sub>PP</sub> | 31  | 35    | 29  | l<br>l | External Access Enable/Programming Supply Voltage: EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to 1FFFH. If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than 1FFFH. This pin also receives the 12.75V programming supply voltage (V <sub>PP</sub> ) during EPROM programming.                                                                        |

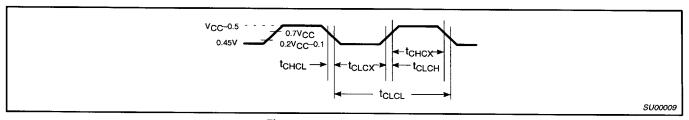

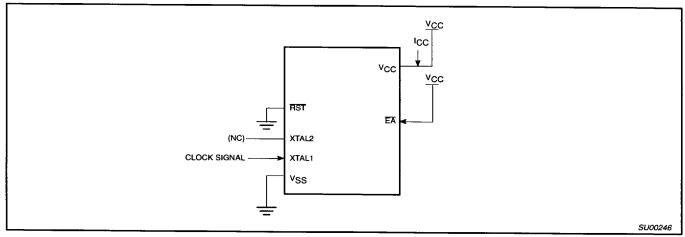

| XTAL1              | 19  | 21    | 15  | 1      | Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                           |

| XTAL2              | 18  | 20    | 14  | 0      | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# 80C575/83C575/87C575

Table 1. 87C575 Special Function Registers

| SYMBOL              | DESCRIPTION                                                     | DIRECT<br>ADDRESS | BIT A  | DDRESS | , SYMBOI   | ., OR ALT | ERNATIV | E PORT     | FUNCTIO    | N<br>LSB   | RESET<br>VALUE |

|---------------------|-----------------------------------------------------------------|-------------------|--------|--------|------------|-----------|---------|------------|------------|------------|----------------|

| ACC*                | Accumulator                                                     | E0H               | E7     | E6     | E5         | E4        | E3      | E2         | E1         | E0         | 00Н            |

| AUXR#               | Auxiliary                                                       | 8EH               | _      | _      | _          | _         | _       |            | LO         | AO         | xxxxxxx00B     |

| B*                  | B register                                                      | F0H               | F7     | F6     | F5         | F4        | F3      | F2         | F1         | F0         | 00Н            |

| CCAP0H#             | Module 0 Capture High                                           | FAH               |        |        |            |           |         |            |            |            | xxxxxxxxB      |

| CCAP1H#             | Module 1 Capture High                                           | FBH               |        |        |            |           |         |            |            |            | xxxxxxxxB      |

| CCAP2H#             | Module 2 Capture High                                           | FCH               |        |        |            |           |         |            |            |            | xxxxxxxxB      |

| CCAP3H#             | Module 3 Capture High                                           | FDH               |        |        |            |           |         |            |            |            | xxxxxxxxB      |

| CCAP4H#             | Module 4 Capture High                                           | FEH               |        |        |            |           |         |            |            |            | xxxxxxxxB      |

| CCAP0L#<br>CCAP1L#  | Module 0 Capture Low<br>Module 1 Capture Low                    | EAH               |        |        |            |           |         |            |            |            | xxxxxxxxB      |

| CCAP1L#             | Module 1 Capture Low                                            | EBH               |        |        |            |           |         |            |            |            | xxxxxxxxB      |

| CCAP3L#             | Module 3 Capture Low                                            | ECH<br>EDH        |        |        |            |           |         |            |            |            | XXXXXXXXB      |

| CCAP4L#             | Module 4 Capture Low                                            | EEH               |        |        |            |           |         |            |            |            | XXXXXXXXB      |

| 33711 4E#           | Module 4 Capture 20W                                            | LLII              |        |        |            |           |         |            |            |            | XXXXXXXXXB     |

| CCAPM0#             | Module 0 Mode                                                   | DAH               | -      | ЕСОМ   | CAPP       | CAPN      | MAT     | TOG        | PWM        | ECCF       | x0000000B      |

| CCAPM1#             | Module 1 Mode                                                   | DBH               | -      | ECOM   | CAPP       | CAPN      | MAT     | TOG        | PWM        | ECCF       | х0000000В      |

| CCAPM2#             | Module 2 Mode                                                   | DCH               |        | ECOM   | CAPP       | CAPN      | MAT     | TOG        | PWM        | ECCF       | x0000000B      |

| CCAPM3#             | Module 3 Mode                                                   | DDH               | _      | ECOM   | CAPP       | CAPN      | MAT     | TOG        | PWM        | ECCF       | х0000000В      |

| CCAPM4#             | Module 4 Mode                                                   | DEH               |        | ECOM   | CAPP       | CAPN      | MAT     | TOG        | PWM        | ECCF       | х0000000В      |

|                     |                                                                 |                   | DF     | DE     | DD         | DC        | DB      | DA         | D9         | D8         |                |

| CCON*#              | PCA Counter Control                                             | D8H               | CF     | CR     | _          | CCF4      | CCF3    | CCF2       | CCF1       | CCF0       | 00x00000B      |

| CH#<br>CL#          | PCA Counter High<br>PCA Counter Low                             | F9H<br>E9H        |        |        |            |           |         |            |            |            | 00Н<br>00Н     |

| CMOD#               | PCA Counter Mode                                                | D9H               | CIDL   | WDTE   | -          | _         |         | CPS1       | CPS0       | ECF        | 00xxx000B      |

|                     |                                                                 |                   | EF     | EE     | ED         | EC        | EB      |            | Ε0.        |            | ]              |

| CMP*#               | Comparator                                                      | E8H               | EC3DP  | EC2DP  | EC1DP      | EC0DP     | C3RO    | EA<br>C2RO | E9<br>C1RO | E8<br>C0RO |                |

| CMPE#               | Comparator Enable                                               | 91H               | EC3TDC | EC2TDC | EC1TDC     | ECOTDC    | EC3OD   | EC2OD      | EC10D      | EC0OD      | 00H            |

| DPTR:<br>DPH<br>DPL | Data Pointer (2 bytes)<br>Data Pointer High<br>Data Pointer Low | 83H<br>82H        | ,      |        |            |           | 20002   | 1 20200    | 10100      |            | 00H            |

|                     |                                                                 |                   | AF     | ΑE     | AD         | AC        | AB      | AA         | A9         | A8         | 0011           |

| IE*                 | Interrupt Enable                                                | A8H               | EA     | EC     | ET2        | ES        | ET1     | EX1        | ЕТО        | EX0        | 00Н            |

|                     | :                                                               |                   | BF     | BE     | BD         | ВС        | BB      | ВА         | B9         | B8         |                |

| IP*                 | Interrupt Priority                                              | В8Н               | _      | PPC    | PT2        | PS        | PT1     | PX1        | PT0        | PX0        | x0000000B      |

|                     |                                                                 |                   | 87     | 86     | 85         | 84        | 83      | 82         | 81         | 80         |                |

| P0*                 | Port 0                                                          | 80H               | AD7    | AD6    | AD5        | AD4       | AD3     | AD2        | AD1        | AD0        | 00Н            |

|                     |                                                                 |                   | 97     | 96     | 95         | 94        | 93      | 92         | 91         | 90         | 1 3311         |

| P1*                 | Port 1                                                          | 90H               | CEX4   | CEX3   | CEX2       | CEX1      | CEX0    | EXI        | T2EX       | T2         | 00Н            |

|                     |                                                                 |                   | A7     | A6     | <b>A</b> 5 | A4        | АЗ      | A2         | A1         | A0         | 1              |

| P2*                 | Port 2                                                          | A0H               | AD15   | AD14   | AD13       | AD12      | AD11    | AD10       | AD9        | AD8        | 00Н            |

|                     |                                                                 |                   | B7     | В6     | B5         | B4        | В3      | B2         | B1         | В0         | 1              |

| P3*                 | Port 3                                                          | вон               | RD     | WR     | T1         | TO        | INT1    | INTO       | TxD        | RxD        | 00H            |

SFRs are bit addressable.

1996 Aug 16

**3110826 0107665 551**

<sup>#</sup> SFRs are modified from or added to the 80C51 SFRs.

Table 1. 87C575 Special Function Registers (Continued)

| SYMBOL               | DESCRIPTION                                 | DIRECT<br>ADDRESS | BIT /<br>MSB | ADDRESS     | , SYMBO          | L, OR AL         | TERNATIV         | E PORT | FUNCTIO           | N<br>LSB | RESET<br>VALUE |

|----------------------|---------------------------------------------|-------------------|--------------|-------------|------------------|------------------|------------------|--------|-------------------|----------|----------------|

| P2OD#                | Port 2 Pullup Disable                       | A1H               |              |             |                  |                  |                  |        |                   |          | 00H            |

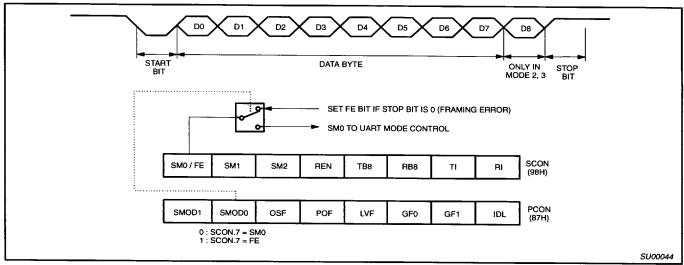

| PCON#                | Power Control                               | 87H               | SMOD1        | SMOD0       | OSF <sup>1</sup> | POF <sup>1</sup> | LVF <sup>1</sup> | GF0    | PD                | IDL      | 00xxx000B      |

|                      |                                             |                   |              |             |                  |                  |                  |        |                   |          |                |

| PSW*                 | Program Status Word                         | DOH               | D7<br>CY     | D6<br>AC    | D5<br>F0         | D4               | D3               | D2     | D1                | D0       |                |

|                      | •                                           |                   | <u> </u>     | AC          | FU               | RS1              | RS0              | ov     | _                 | Р        | 00H            |

| RACAP2H#<br>RACAP2L# | Timer 2 Capture High<br>Timer 2 Capture Low | CBH<br>CAH        | 1            |             |                  |                  |                  |        |                   |          | 00H            |

| NAUAF2L#             | Timer 2 Capture Low                         | CAH               |              |             |                  |                  |                  |        |                   |          | 00H            |

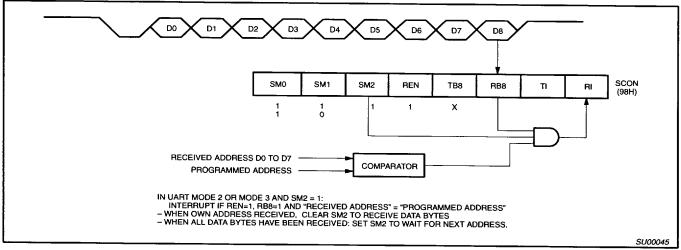

| SADDR#               | Slave Address                               | A9H               |              |             |                  |                  |                  |        |                   |          | 00Н            |

| SADEN#               | Slave Address Mask                          | В9Н               |              |             |                  |                  |                  |        |                   |          | 00H            |

|                      |                                             |                   |              |             |                  |                  |                  |        |                   |          |                |

| SBUF                 | Serial Data Buffer                          | 99H               | }            |             |                  |                  |                  |        |                   |          | xxxxxxxxB      |

|                      |                                             |                   | 9F           | 9E          | 9D               | 9C               | 9B               | 9A     | 99                | 98       |                |

| SCON*                | Serial Control                              | 98H               | SM0          | SM1         | SM2              | REN              | TB8              | RB8    | TI                | RI       | 00Н            |

| SP                   | Stack Pointer                               | 81H               |              |             |                  |                  |                  |        |                   |          | 07H            |

|                      |                                             |                   | 8F           | 8E          | 8D               | 8C               | 8B               | 8A     | 89                | 88       | <b>[</b>       |

| TCON*                | Timer Control                               | 88H               | TF1          | TR1         | TF0              | TR0              | IE1              | IT1    | IEO               | IT0      | оон            |

|                      |                                             |                   |              | <del></del> |                  |                  |                  |        |                   |          | 1              |

|                      |                                             |                   | CF           | CE          | CD               | cc               | СВ               | CA     | C9                | C8       |                |

| T2CON*               | Timer 2 Control                             | C8H               | TF2          | EXF2        | RCLK             | TCLK             | EXEN2            | TR2    | C/T2              | CP/RL2   | 00H            |

| T2MOD#               | Timer 2 Mode Control                        | C9H               |              | -           |                  | <u> </u>         |                  | _      | T2OE <sup>2</sup> | DCEN     | xxxxxxx0B      |

| THO                  | Timer High 0                                | 8CH               |              |             |                  |                  |                  |        |                   |          | 00H            |

| TH1                  | Timer High 1                                | 8DH               |              |             |                  |                  |                  |        |                   |          | 00H            |

| TH2#                 | Timer High 2                                | CDH               |              |             |                  |                  |                  |        |                   |          | 00H            |

| TLO                  | Timer Low 0                                 | 8AH               |              |             |                  |                  |                  |        |                   |          | 00H            |

| TL1                  | Timer Low 1                                 | 8BH               |              |             |                  |                  |                  |        |                   |          | 00H            |

| TL2#                 | Timer Low 2                                 | ССН               |              |             |                  |                  |                  |        |                   |          | 00H            |

| TMOD                 | Timer Mode                                  | 89H               | GATE         | C/T         | M1               | MO               | GATE             | С/Т    | M1                | MO       | 00Н            |

|                      |                                             | 1                 | C7           | C6          | C5               | C4               | C3               | C2     | C1                | CO       | 1              |

| WDCON*#              | Watchdog Timer Control                      | СОН               | PRE2         | PRE1        | PRE0             | LVRE             | OFRE             | WDRUN  | WDTOF             | WDMOD    | 11111101B      |

| WDL#                 | Watchdog Timer Reload                       | C1H               |              | -           | •                |                  |                  | •      |                   | •        | 00H            |

| WFEED1#              | Watchdog Feed 1                             | C2H               |              |             |                  |                  |                  |        |                   |          | xxH            |

| WFEED2#              | Watchdog Feed 2                             | СЗН               |              |             |                  |                  |                  |        |                   |          | xxH            |

SFRs are bit addressable.

SFRs are modified from or added to the 80C51 SFRs.

Reset value depends on reset source.

Programmable clock-out.

### 80C575/83C575/87C575

#### **POWER ON CLEAR/ POWER ON FLAG**

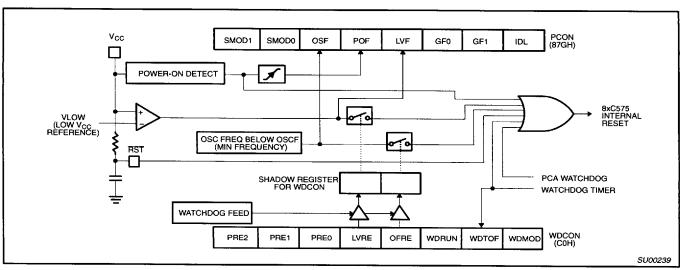

An on-chip Power On Detect Circuit resets the 8XC575 and sets the Power Off Flag (PCON.4) on power up or if V<sub>CC</sub> drops to zero momentarily. The POF can only be cleared by software. The RST pin is not driven by the power on detect circuit. The POF can be read by software to determine that a power failure has occurred and can also be set by software.

#### **LOW VOLTAGE DETECT**

An on-chip Low Voltage Detect circuit sets the Low Voltage Flag (PCON.3) if V<sub>CC</sub> drops below V<sub>LOW</sub> (see DC Electrical Characteristics) and resets the 8XC575 if the Low Voltage Reset Enable bit (WDCON.4) is set. If the LVRE is cleared, the reset is disabled but LVF will still be set if  $V_{CC}$  is low. The RST pin is not driven by the low voltage detect circuit. The LVF can be read by software to determine that V<sub>CC</sub> was low. The LVF can be set or cleared by software.

#### OSCILLATOR FAIL DETECT

An on-chip Oscillator Fail Detect circuit sets the Oscillator Fail Flag (PCON.5) if the oscillator frequency drops below OSCF for one or more cycles (see AC Electrical Characteristics: OSCF) and resets the 8XC575 if the Oscillator Fail Reset Enable bit (WDCON.3) is set. If OFRE is cleared, the reset is disabled but OSF will still be set if the oscillator fails. The RST pin is not driven by the oscillator fail detect circuit. The OSF can be read by software to determine that an oscillator failure has occurred. The OSF can be set or cleared by software.

#### **LOW ACTIVE RESET**

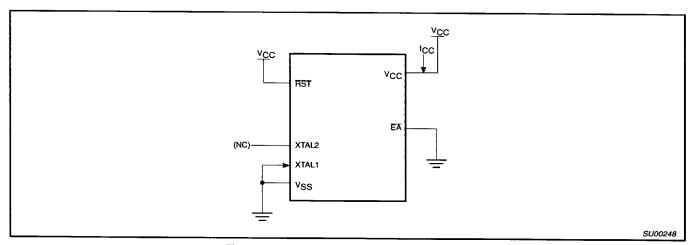

One of the most notable features on this part is the low active reset. At this time this is the only 80C51 derivative available that has low active reset. This feature makes it easier to interface the 8XC575 into an application to accommodate the power-on and low voltage conditions that can occur. The low active reset operates exactly the same as high active reset with the exception that the part is put into the reset mode by applying a low level to the reset pin. For power-on reset it is also necessary to invert the power-on reset circuit; connecting the 8.2K resistor from the reset pin to V<sub>CC</sub> and the 10µf capacitor from the reset pin to ground. Figure 1 shows all of the reset related circuitry.

When reset the port pins on the 87C575 are driven low asynchronously. This is different from all other 80C51 derivatives.

The 8XC575 also has Low voltage detection circuitry that will, if enabled, force the part to reset when V<sub>CC</sub> (on the part) fails below a set level. Low Voltage Reset is enabled by a normal reset. Low Voltage Reset can be disabled by clearing LVRE (bit 4 in the WDCON SFR) then executing a watchdog feed sequence (A5H to WFEED1 followed immediately by 5A to WFEED2). In addition there is a flag (LVF) that is set if a low voltage condition is detected. The LVF flag is set even if the Low Voltage detection circuitry is disabled. Notice that the Low voltage detection circuitry does not drive the RST# pin so the LVF flag is the only way that the microcontroller can determine if it has been reset due to a low voltage condition.

The 8XC575 has an on-chip power-on detection circuit that sets the POF (PCON.4) flag on power up or if the  $V_{CC}$  level momentarily drops to 0V. This flag can be used to determine if the part is being started from a power-on (cold start) or if a reset has occurred due to another condition (warm start).

#### **TIMERS**

The 87C575 has four on-chip timers.

Timers 0 and 1 are identical in every way to Timers 0 and 1 on the 80C51.

Timer 2 on the 8XC575 is identical to the 80C52 Timer 2 (described in detail in the 80C52 overview) with the exception that it is an up or down counter. To configure the Timer to count down the DCEN bit in the T2MOD special function register must be set and a low level must be present on the T2EX pin (P1.1).

The Watchdog timer operation and implementation is the same as that for the 8XC550 (described in the 8XC550 overview) with the exception that the reset values of the WDCON and WDL special function registers have been changed. The changes in these registers cause the watchdog timer to be enabled with a timeout of 98304 × TOSC when the part is reset. The watchdog can be disabled by executing a valid feed sequence and then clearing WDRUN (bit 2 in the WDCON SFR).

Figure 1. Reset Circuitry

1996 Aug 16

9

7110826 0107667 324

### 80C575/83C575/87C575

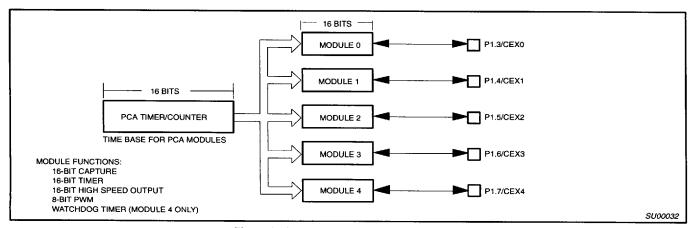

# PROGRAMMABLE COUNTER ARRAY (PCA)

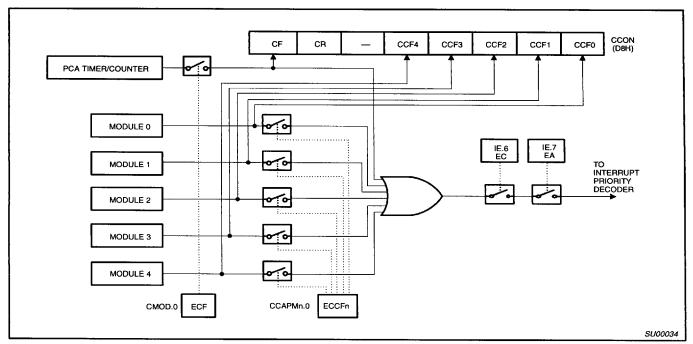

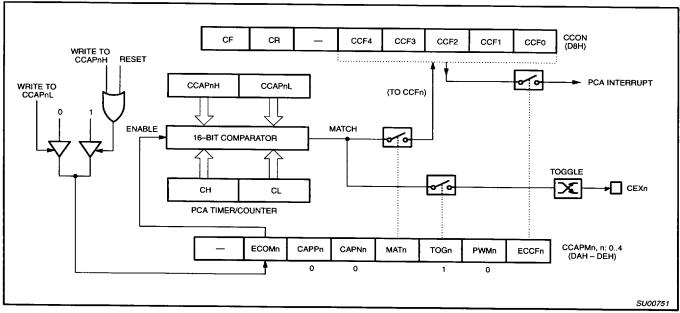

The Programmable Counter Array is a special Timer that has five 16-bit capture/compare modules associated with it. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or pulse width modulator. Each module has a pin associated with it in port 1. Module 0 is connected to P1.3(CEX0), module 1 to P1.4(CEX1), etc.. The basic PCA configuration is shown in Figure 2.

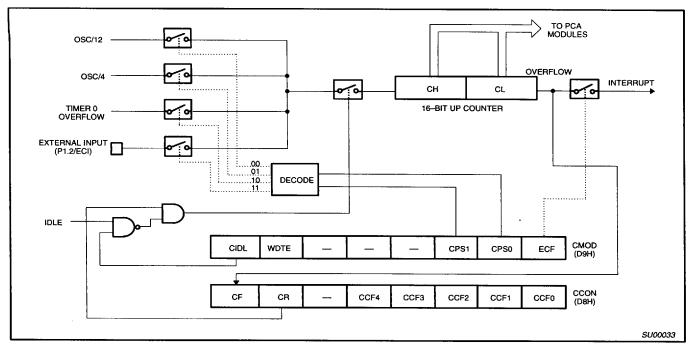

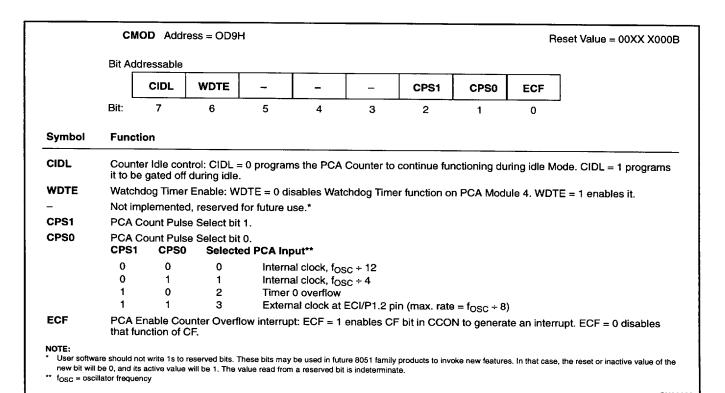

The PCA timer is a common time base for all five modules and can be programmed to run at: 1/12 the oscillator frequency, 1/4 the oscillator frequency, the Timer 0 overflow, or the input on the ECI pin (P1.2). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD SFR as follows (see Figure 3):

#### **CPS1 CPS0 PCA Timer Count Source**

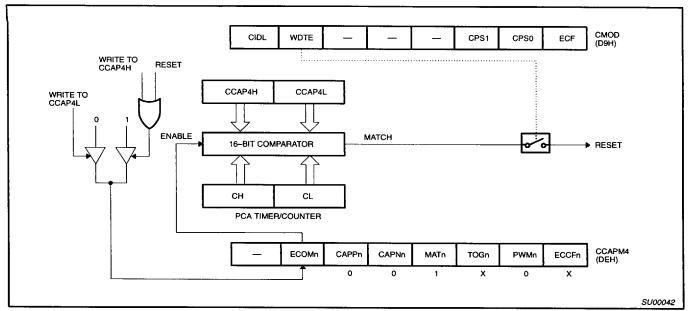

In the CMOD SFR are three additional bits associated with the PCA. They are CIDL which allows the PCA to stop during idle mode, WDTE which enables or disables the watchdog function on module 4, and ECF which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows. These functions are shown in Figure 3.

The watchdog timer function is implemented in module 4 as implemented in other parts that have a PCA that are available on the market. However, if a watchdog timer is required in the target application, it is recommended to use the hardware watchdog timer that is implemented on the 87C575 separately from the PCA (see Figure 14).

The CCON SFR contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (refer to Figure 6). To run the PCA the CR bit (CCON.6) must be set by software. The PCA is shut off by clearing this bit. The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set, The CF bit can only be cleared by software. Bits 0 through 4 of the CCON register are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software. The PCA interrupt system shown in Figure 4.

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (see Figure 7). The registers contain the bits that control the mode that each module will operate in. The ECCF bit (CCAPMn.0 where n=0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module. PWM (CCAPMn.1) enables the pulse width modulation mode. The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register. The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition. The last bit in

the register ECOM (CCAPMn.6) when set enables the comparator function. Figure 8 shows the CCAPMn settings for the various PCA functions.

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output.

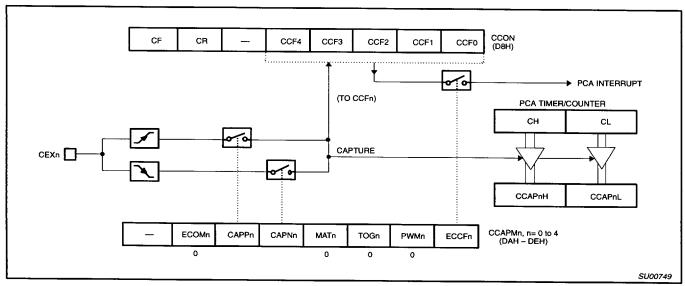

#### **PCA Capture Mode**

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated. Refer to Figure 9.

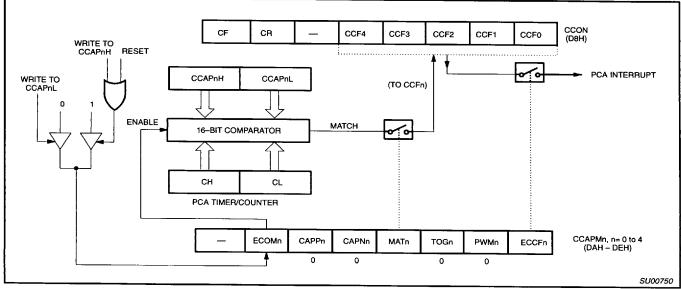

#### 16-bit Software Timer Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (see Figure 10).

#### **High Speed Output Mode**

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (see Figure 11).

Figure 2. Programmable Counter Array (PCA)

1996 Aug 16

10

**7110826 0107668 260**

Figure 3. PCA Timer/Counter

Figure 4. PCA Interrupt System

Figure 5. CMOD: PCA Counter Mode Register

|                                      | Bit Ad                            | dressable                                                |                                                                  |                                                          |                                                          |                                              |                                              |                                           |                                              |                                  |

|--------------------------------------|-----------------------------------|----------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------------|----------------------------------------------|----------------------------------|

|                                      |                                   | CF                                                       | CR                                                               | -                                                        | CCF4                                                     | CCF3                                         | CCF2                                         | CCF1                                      | CCF0                                         | ]                                |

|                                      | Bit:                              | 7                                                        | 6                                                                | 5                                                        | 4                                                        | 3                                            | 2                                            | 1                                         | 0                                            | J                                |

| Symbol                               | Funct                             | tion                                                     |                                                                  |                                                          |                                                          |                                              |                                              |                                           |                                              |                                  |

| CF                                   | PCA (<br>set. C                   | Counter Ov                                               | verflow flag<br>set by eithe                                     | Set by ha                                                | rdware whe                                               | n the count                                  | er rolls over                                | : CF flags a                              | n interrupt                                  | if bit ECF in CMOD is            |

| CR                                   |                                   | Counter Ru                                               |                                                                  |                                                          |                                                          |                                              |                                              | -                                         |                                              | oftware to turn the PCA          |

|                                      |                                   |                                                          |                                                                  |                                                          |                                                          |                                              |                                              |                                           |                                              |                                  |

| _                                    |                                   | plemented                                                | d, reserved                                                      | for future (                                             | use*.                                                    |                                              |                                              |                                           |                                              |                                  |

| –<br>CCF4                            | Not in                            | -                                                        |                                                                  |                                                          |                                                          | en a match o                                 | or capture c                                 | occurs. Mus                               | t be cleared                                 | d bv software.                   |

|                                      | Not in<br>PCA                     | Module 4 ir                                              | nterrupt flag                                                    | . Set by ha                                              | ardware whe                                              |                                              |                                              |                                           |                                              | d by software.<br>d by software. |

| CCF3                                 | Not in<br>PCA I<br>PCA I          | Module 4 ir<br>Module 3 ir                               | nterrupt flag<br>nterrupt flag                                   | . Set by ha                                              | ardware whe<br>ardware whe                               | n a match                                    | or capture c                                 | occurs. Mus                               | t be cleared                                 | d by software.                   |

| CCF3<br>CCF2                         | Not in<br>PCA I<br>PCA I<br>PCA I | Module 4 ir<br>Module 3 ir<br>Module 2 ir                | nterrupt flag<br>nterrupt flag<br>nterrupt flag                  | . Set by ha<br>. Set by ha<br>. Set by ha                | ardware whe<br>ardware whe<br>ardware whe                | en a match e<br>en a match e                 | or capture o<br>or capture o                 | occurs. Mus<br>occurs. Mus                | t be cleared<br>t be cleared                 | d by software.<br>d by software. |

| CCF4<br>CCF3<br>CCF2<br>CCF1<br>CCF0 | Not in<br>PCA I<br>PCA I<br>PCA I | Module 4 ir<br>Module 3 ir<br>Module 2 ir<br>Module 1 ir | nterrupt flag<br>nterrupt flag<br>nterrupt flag<br>nterrupt flag | . Set by ha<br>. Set by ha<br>. Set by ha<br>. Set by ha | ardware whe<br>ardware whe<br>ardware whe<br>ardware whe | en a match e<br>en a match e<br>en a match e | or capture c<br>or capture c<br>or capture c | occurs. Mus<br>occurs. Mus<br>occurs. Mus | t be cleared<br>t be cleared<br>t be cleared | d by software.                   |

Figure 6. CCON: PCA Counter Control Register

|               |                  | CCAI<br>CCAI<br>CCAI | PM2 0D0                        | ËH                          |             |                                       |              |             |              | eset Value = X000 0000B |

|---------------|------------------|----------------------|--------------------------------|-----------------------------|-------------|---------------------------------------|--------------|-------------|--------------|-------------------------|

|               |                  | CCA                  |                                |                             |             |                                       |              |             |              |                         |

|               | Not Bit          | Addressa             | able                           |                             |             |                                       |              |             |              |                         |

|               |                  | -                    | ECOMn                          | CAPPn                       | CAPNn       | MATn                                  | TOGn         | PWMn        | ECCFn        | ]                       |

|               | Bit:             | 7                    | 6                              | 5                           | 4           | 3                                     | 2            | 1           | 0            | J                       |

| Symbol        | Funct            | ion                  |                                |                             |             |                                       |              |             |              |                         |

| _             | Not im           | plemente             | ed, reserved                   | for future u                | se*.        | · · · · · · · · · · · · · · · · · · · |              |             |              |                         |

| <b>ECOM</b> n |                  |                      | rator. ECOM                    |                             |             | parator fund                          | ction.       |             |              |                         |

| CAPPn         |                  |                      | re, CAPPn =                    |                             | -           |                                       |              |             |              |                         |

| CAPNn         | Captu            | re Negati            | ve, CAPNn :                    | = 1 enables                 | negative e  | dge capture                           | ).           |             |              |                         |

| MATn          | Match<br>in CC   | . When M<br>ON to be | fATn = 1, a r<br>set, flagging | natch of the<br>an interrup | e PCA coun  | ter with this                         | module's o   | compare/ca  | pture regist | er causes the CCFn bit  |

| TOGn          | Toggle<br>pin to | e. When T<br>toggle. | ГОGn = 1, а                    | match of th                 | e PCA cour  | nter with thi                         | s module's   | compare/ca  | apture regis | ter causes the CEXn     |

| PWMn          | Pulse            | Width Mo             | odulation Mo                   | de. PWMn                    | = 1 enables | the CEXn                              | pin to be us | sed as a pu | lse width m  | odulated output.        |

|               |                  |                      | terrupt. Enat                  |                             |             |                                       |              |             |              |                         |

| <b>ECCFn</b>  |                  |                      |                                |                             |             |                                       |              | _           | _            | ·                       |

Figure 7. CCAPMn: PCA Modules Compare/Capture Registers

|   | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn | MODULE FUNCTION                                   |

|---|-------|-------|-------|------|------|------|-------|---------------------------------------------------|

| Х | 0     | 0     | 0     | 0    | 0    | 0    | 0     | No operation                                      |

| Х | Х     | 1     | 0     | 0    | 0    | 0    | Х     | 16-bit capture by a positive-edge trigger on CEXn |

| × | Х     | 0     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a negative trigger on CEXn      |

| × | Х     | 1     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a transition on CEXn            |

| Х | 1     | 0     | 0     | 1    | 0    | 0    | X     | 16-bit Software Timer                             |

| × | 1     | 0     | 0     | 1    | 1    | 0    | х     | 16-bit High Speed Output                          |

| × | 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |

| X | 1     | 0     | 0     | 1    | Х    | 0    | X     | Watchdog Timer                                    |

Figure 8. PCA Module Modes (CCAPMn Register)

Figure 9. PCA Capture Mode

Figure 10. PCA Compare Mode

### 80C575/83C575/87C575

Figure 11. PCA High Speed Output Mode

#### **Pulse Width Modulator Mode**

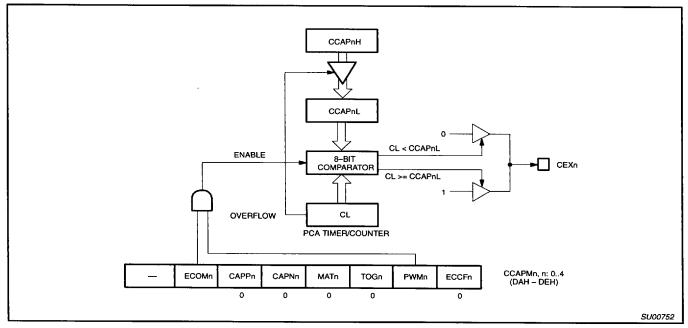

All of the PCA modules can be used as PWM outputs. Figure 12 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

#### **WATCHDOG TIMER**

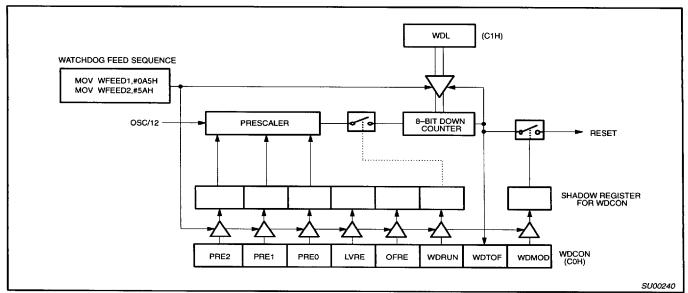

The watchdog timer is not directly loadable by the user. Instead, the value to be loaded into the main timer is held in an autoload register or is part of the mask ROM programming. In order to cause the main timer to be loaded with the appropriate value, a special sequence of software action must take place. This operation is referred to as feeding the watchdog timer.

To feed the watchdog, two instructions must be sequentially executed successfully. No

intervening instruction fetches are allowed, so interrupts should be disabled before feeding the watchdog. The instructions should move A5H to the WFEED1 register and then 5AH to the WFEED2 register. If WFEED1 is correctly loaded and WFEED2 is not correctly loaded, then an immediate underflow will occur.

The watchdog timer subsystem has two modes of operation. Its principal function is a watchdog timer. In this mode it protects the system from incorrect code execution by causing a system reset when the watchdog timer underflows as a result of a failure of software to feed the timer prior to the timer reaching its terminal count. If the user does not employ the watchdog function, the watchdog subsystem can be used as a timer. In this mode, reaching the terminal count sets a flag. In most other respects, the timer mode possesses the characteristics of the watchdog mode. This is done to protect the integrity of the watchdog function.

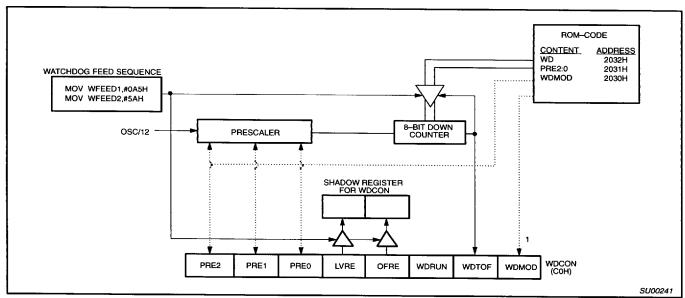

The watchdog timer subsystem consists of a prescaler and a main counter. The prescaler has 8 selectable taps off the final stages and the output of a selected tap provides the clock to the main counter. The main counter is the section that is loaded as a result of the software feeding the watchdog and it is the section that causes the system reset

(watchdog mode) or time-out flag to be set (timer mode) if allowed to reach its terminal count.

**Programming the Watchdog Timer** Both the EPROM and ROM devices have a set of SFRs for holding the watchdog autoload values and the control bits. The watchdog time-out flag is present in the watchdog control register and operates the same in all versions. In the EPROM device, the watchdog parameters (autoload value and control) are always taken from the SFRs. In the ROM device, the watchdog parameters can be mask programmed or taken from the SFRs. The selection to take the watchdog parameters from the SFRs or from the mask programmed values is controlled by EA (external access). When EA is high (internal ROM access), the watchdog parameters are taken from the mask programmed values. If the watchdog is mask programmed to the timer mode, then the autoload values and the pre-scaler taps are taken from the SFRs. When EA is low (external access), the watchdog parameters are taken from the SFRs. The user should be able to leave code in his program which initializes the watchdog SFRs even though he has migrated to the mask ROM part. This allows no code changes from EPROM prototyping to ROM coded production parts.

1996 Aug 16

15

7110826 0107673 628 📟

### 80C575/83C575/87C575

Figure 12. PCA PWM Mode

### **Watchdog Detailed Operation**

# EPROM Device (and ROMless Operation: EA = 0)

In the ROMless operation (ROM part,  $\overline{EA} = 0$ ) and in the EPROM device, the watchdog operates in the following manner (see Figure 14).

Whether the watchdog is in the watchdog or timer mode, when external RESET is applied, the following takes place:

- Watchdog mode bit set to watchdog mode.

- Watchdog run control bit set to ON.

- Autoload register set to 00 (min. count).

- Watchdog time-out flag cleared.

- Prescaler is cleared.

- Prescaler tap set to the highest divide.

- Autoload takes place.

The watchdog can be fed even though it is in the timer mode.

Note that the operational concept is for the watchdog mode of operation, when coming out of a hardware reset, the software should load the autoload registers, set the mode to watchdog, and then feed the watchdog (cause an autoload). The watchdog will now be starting at a known point.

If the watchdog is in the watchdog mode and running and happens to underflow at the time

the external RESET is applied, the watchdog time-out flag will be cleared.

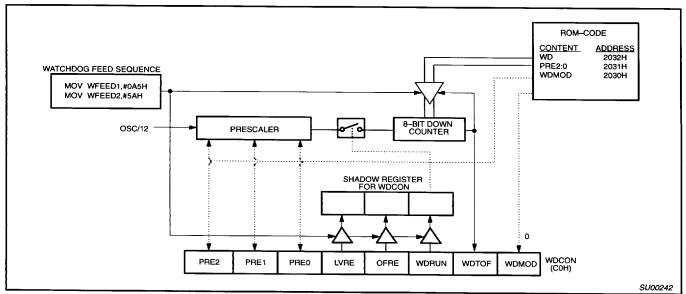

When the watchdog is in the watchdog mode and the watchdog underflows, the following action takes place (see Figure 16):

- Autoload takes place.

- Watchdog time-out flag is set

- Mode bit unchanged.

- Watchdog run bit unchanged.

- Autoload register unchanged.

- Prescaler tap unchanged.

- All other device action same as external reset.

Note that if the watchdog underflows, the program counter will start from 00H as in the case of an external reset. The watchdog time-out flag can be examined to determine if the watchdog has caused the reset condition. The watchdog time-out flag bit can be cleared by software.

When the watchdog is in the timer mode and the timer software underflows, the following action takes place:

- Autoload takes place.

- Watchdog time-out flag is set

- Mode bit unchanged.

- Watchdog run bit unchanged.

- Autoload register unchanged.

- Prescaler tap unchanged.

#### Mask ROM Device (EA = 1)

In the mask ROM device, the watchdog mode bit (WDMOD) is mask programmed and the bit in the watchdog command register is read only and reflects the mask programmed selection. If the mask programmed mode bit selects the timer mode, then the watchdog run bit (WDRUN) operates as described under EPROM Device. If the mask programmed bit selects the watchdog mode, then the watchdog run bit has no effect on the timer operation (see Figure 15).

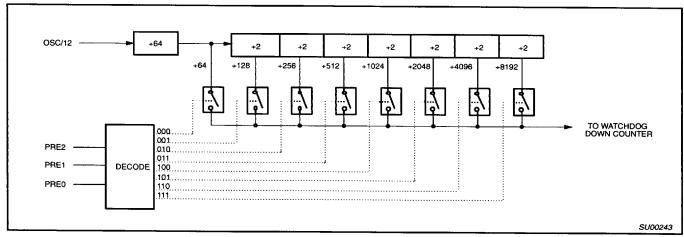

#### **Watchdog Function**

The watchdog consists of a programmable prescaler and the main timer. The prescaler derives its clock from the on-chip oscillator. The prescaler consists of a divide by 12 followed by a 13 stage counter with taps from stage 6 through stage 13. This is shown in Figure 17. The tap selection is programmable. The watchdog main counter is a down counter clocked (decremented) each time the programmable prescaler underflows. The watchdog generates an underflow signal (and is autoloaded) when the watchdog is at count 0 and the clock to decrement the watchdog occurs. The watchdog is 8 bits long and the autoload value can range from 0 to FFH. (The

1996 Aug 16

16

| 7110826 0107674 564 📟

### 80C575/83C575/87C575

autoload value of 0 is permissible since the prescaler is cleared upon autoload).

This leads to the following user design equations. Definitions :t\_{OSC} is the oscillator period, N is the selected prescaler tap value, W is the main counter autoload value,  $t_{MIN}$  is the minimum watchdog time-out value (when the autoload value is 0),  $t_{MAX}$  is the maximum time-out value (when the autoload value is FFH),  $t_{D}$  is the design time-out value.

$t_{MIN} = t_{OSC} \times 12 \times 64$

$t_{MAX} = t_{MIN} \times 128 \times 256$

$t_D = t_{MIN} \times 2^{PRESCALER} \times (W + 1)$ (where prescaler = 0, 1, 2, 3, 4, 5, 6, or 7)

Note that the design procedure is anticipated to be as follows. A  $t_{MAX}$  will be chosen either from equipment or operation considerations and will most likely be the next convenient value higher than  $t_D$ . (If the watchdog were inadvertently to start from FFH, an overflow would be guaranteed, barring other anomalies, to occur within  $t_{MAX}$ ). Then the value for the prescaler would be chosen from:

prescaler = log2 ( $t_{MAX}$  / ( $t_{OSC} \times 12 \times 256$ )) - 6

This then also fixes  $t_{\mbox{\scriptsize MIN}}$ . An autoload value would then be chosen from:

$W = t_D / t_{MIN} - 1$

The software must be written so that a feed operation takes place every  $t_{\rm D}$  seconds from the last feed operation. Some tradeoffs may need to be made. It is not advisable to include feed operations in minor loops or in subroutines unless the feed operation is a specific subroutine.

# Watchdog Control Register (WDCON) (Bit Addressable) Address C0

The following bits of this register are read only in the ROM part when EA is high: WDMOD, PRE0, PRE1, and PRE2. That is, the register will reflect the mask programmed values. In the ROM part with EA high, these bits are taken from mask coded bits and are not readable by the program. WDRUN is

read only in the ROM part when EA is high and WDMOD is in the watchdog mode. When WDMOD is in the timer mode, WDRUN functions normally.