# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

### MCM62974A

### Product Preview

# 4K × 12 Bit Synchronous Static RAM with Output Registers and Output Enable

The MCM62974A is a 49,152 bit synchronous static random access memory organized as 4096 words of 12 bits, fabricated using Motorola's second-generation high-performance silicon-gate CMOS (HCMOS III) technology. The device integrates input registers, high speed SRAM, and high-drive capability output registers onto a single monolithic circuit for reduced parts count implementation of cache data RAM, writeable control store applications, and other applications that utilize long words.

Synchronous design allows precise cycle control with the use of an external clock (K), while CMOS circuitry reduces the overall power consumption of the integrated functions for greater reliability.

The address (A0-A11), data (D0-D11), and write  $(\overline{W})$  inputs are all clock (K) controlled, positive-edge-triggered, noninverting registers.

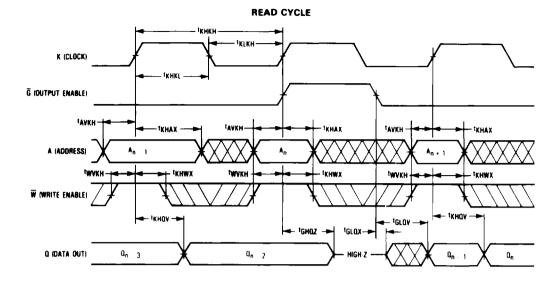

The MCM62974A provides output register operation. At the rising edge of clock (K), the RAM data from the previous clock (K) high cycle is presented.

The output enable (G) provides asynchronous bus control for common I/O or bank switch applications.

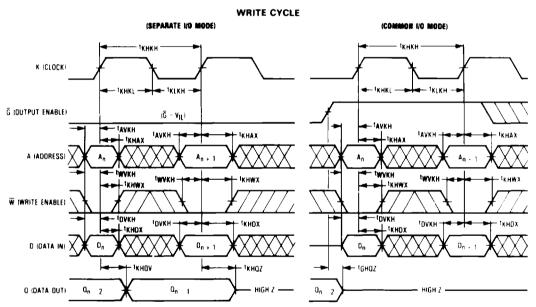

Write operations are internally self-timed and initiated by the rising edge of the clock (K) input. This feature eliminates complex off-chip write pulse generation and provides increased flexibility for incoming signals.

- Single 5 V ± 10% Power Supply

- Fast Cycle Times: 18/20 ns Max

- Fast Clock (K) Access Times: 10/10 ns Max

- Address, Data Input, and W Registers On-Chip

- Output Enable for Asynchronous Bus Control

- Output Registers for Fully Pipelined Applications

- High Output Drive Capability

- Internally Self-Timed Write Pulse Generation

- Separate Data Input and Data Output Pins

#### PIN ASSIGNMENT

|                        | BLOCK DIAGRAM   |                                          |     |

|------------------------|-----------------|------------------------------------------|-----|

| ADDRESS REGISTERS      | DECODERS • MEMO | IK × 12  DRY MATRIX ROWS ×  VSS  VSS0    |     |

| DD-D11 DATA REGISTERS  | 384             | COLUMNS                                  | ao  |

| WAITE ENABLE REGISTER  |                 | LUMN 110 OLUMN CODERS OUTPUT REGISTERS   | •   |

| K - CLOCK INPUT        | ucaena (on      | -{}                                      | 011 |

| G OUTPUT ENABLE BUFFER |                 | 12, A1, A0, A6<br>11, A10, A9, A8<br>LSB | †   |

| PIN NAMES                             |  |  |  |  |  |  |

|---------------------------------------|--|--|--|--|--|--|

| A0-A11 Address Inputs                 |  |  |  |  |  |  |

| W Write Enable                        |  |  |  |  |  |  |

| G Output Enable                       |  |  |  |  |  |  |

| D0-D11 Data Inputs                    |  |  |  |  |  |  |

| Q0-Q11 Data Outputs                   |  |  |  |  |  |  |

| K Clock Input                         |  |  |  |  |  |  |

| VCC +5 V Power Supply                 |  |  |  |  |  |  |

| V <sub>SS</sub> Ground                |  |  |  |  |  |  |

| V <sub>SSQ</sub> Output Buffer Ground |  |  |  |  |  |  |

For proper operation of the device VSS and both VSSQ leads must be connected to ground.

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice

#### TRUTH TABLE

| ₩ | Operation | O0-O9  | Current |  |

|---|-----------|--------|---------|--|

| L | Write     | High Z | ICCA    |  |

| Н | Read      | Dout   | ICCA    |  |

NOTE: The value  $\overline{\mathbf{W}}$  is a valid input for the setup and hold times relative to the K rising edge.

#### ABSOLUTE MAXIMUM RATINGS (Voltages referenced to VSS = VSSQ = 0 V)

| Rating                                                 | Symbol                             | Value                        | Unit |

|--------------------------------------------------------|------------------------------------|------------------------------|------|

| Power Supply Voltage                                   | Vcc                                | -0.5 to +7.0                 | ٧    |

| Voltage Relative to VSS/VSSQ for Any<br>Pin Except VCC | V <sub>in</sub> , V <sub>out</sub> | -0.5 to V <sub>CC</sub> +0.5 | >    |

| Output Current (per I/O)                               | lout                               | ± 20                         | mA   |

| Power Dissipation (T <sub>A</sub> = 25°C)              | PD                                 | 1.0                          | w    |

| Temperature Under Bias                                 | T <sub>bias</sub>                  | - 10 to +85                  | °C   |

| Operating Temperature                                  | TA                                 | 0 to +70                     | °C   |

| Storage Temperature                                    | T <sub>stg</sub>                   | - 55 to + 125                | °C   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

This is a synchronous device. All synchronous inputs must meet the specified setup and hold times with stable logic levels for ALL rising edges of clock (K) while the device is selected.

This device contains circuitry that will ensure the output devices are in High Z at power up. Care should be taken by the user to ensure that all clocks are at V<sub>IL</sub> or V<sub>IH</sub> during power up to prevent spurious read cycles from occurring.

This CMOS memory circuit has been designed to meet the dc and ac specifications shown in the tables, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow of at least 500 linear feet per minute is maintained.

#### DC OPERATING CONDITIONS AND CHARACTERISTICS

$(V_{CC} = 5.0 \text{ V } \pm 10\%, \text{ T}_{A} = 0 \text{ to } 70^{\circ}\text{C}, \text{ Unless Otherwise Noted})$

#### RECOMMENDED OPERATING CONDITIONS (Voltages referenced to VSS = VSSQ = 0 V)

| Parameter                                | Symbol | Min    | Тур | Max                  | Unit |

|------------------------------------------|--------|--------|-----|----------------------|------|

| Supply Voltage (Operating Voltage Range) | VCC    | 4.5    | 5.0 | 5.5                  | V    |

| Input High Voltage                       | VIH    | 2.2    | -   | V <sub>CC</sub> +0.3 | V    |

| Input Low Voltage                        | VIL    | - 0.5* |     | 0.8                  | V    |

$V_{II}$  (min) = -3.0 V ac (pulse width  $\leq$  20 ns)

#### DC CHARACTERISTICS

| Parameter                                                                                                                                                                                                        |        | Min | Max        | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|------------|------|

| Input Leakage Current (All Inputs, Vin = 0 to VCC)                                                                                                                                                               |        | -   | ± 1.0      | μΑ   |

| Output Leakage Current ( $\overline{G} = V_{IH}$ , $V_{Out} = 0$ to $V_{CC}$ , Outputs must be high-Z)                                                                                                           | lkg(O) | ~   | ± 1.0      | μΑ   |

| AC Supply Current, All Inputs = V <sub>IL</sub> or V <sub>IH</sub> , I <sub>out</sub> = 0 mA, Cycle Time ≥t <sub>KHKH</sub> minI MCM62974A⋅18: t <sub>KHKH</sub> = 18 ns MCM62974A⋅20: t <sub>KHKH</sub> = 20 ns |        |     | 180<br>170 | mA   |

| Output Low Voltage (I <sub>OL</sub> = 12.7 mA)                                                                                                                                                                   |        | -   | 0.4        | v    |

| Output High Voltage (I <sub>OH</sub> = -1.8 mA)                                                                                                                                                                  | Voн    | 2.8 | -          | V    |

#### CAPACITANCE (f = 1.0 MHz, dV = 3.0 V, T<sub>A</sub> = 25°C, Periodically Sampled Rather Than 100% Tested)

| Characteristic     |      | Тур | Max | Unit |

|--------------------|------|-----|-----|------|

| Input Capacitance  | Cin  | 3   | 4   | pF   |

| Output Capacitance | Cout | 5   | 7   | pF   |

#### AC OPERATING CONDITIONS AND CHARACTERISTICS

$(V_{CC} = 5.0 \text{ V} \pm 10\%, T_A = 0 \text{ to } +70^{\circ}\text{C}, \text{ Unless Otherwise Noted})$

| Input Timing Measurement Reference Level 1.5 V | Output Timing Measurement Reference Level 1.5 V |

|------------------------------------------------|-------------------------------------------------|

| Input Pulse Levels                             | Output LoadSee Figure 1A Unless Otherwise Noted |

| Input Rise/Fall Time                           |                                                 |

#### READ/WRITE CYCLE

| Parameter                             |             |                         | MCM62974A-18 |     | MCM62974A-20 |     | 141.    |         |

|---------------------------------------|-------------|-------------------------|--------------|-----|--------------|-----|---------|---------|

|                                       |             | Symbol                  | Min          | Max | Min          | Max | Unit    | Notes   |

| Read Cycle Time                       |             | tKHKH                   | 18           |     | 20           | _   | กร      | 1, 3    |

| Write Cycle Time                      |             | tKHKH                   | 18           | T - | 20           | -   | ns      | 2, 3    |

| Clock High Access Time                |             | tKHQV                   | _            | 10  | _            | 10  | ns      | 3, 4    |

| G Low to Output Valid                 |             | †GLQV                   | _            | 10  | _            | 10  | ns      | 3       |

| Output Active from Clock High         |             | tkHQX                   | 0            |     | 0            | _   | ns      |         |

| Output Active from G Low              |             | †GLQX                   | 0            | _   | 0            | _   | ns      |         |

| Clock Low Pulse Width                 |             | tKLKH                   | 5            | -   | 5            | _   | ns      |         |

| Clock High Pulse Width                |             | tKHKL                   | 5            | _   | 5            |     | ns      |         |

| Setup Times for:                      | A<br>D<br>₩ | tavkh<br>tdvkh<br>twvkh | 4            | _   | 4            | -   | ns      | 1, 2, 5 |

| Hold Times for:                       | A<br>D<br>W | tKHAX<br>tKHDX<br>tKHWX | 2            | _   | 2            | ns  | 1, 2, 5 |         |

| Clock High to Output High Z (W = VIL) |             | tKHQZ                   | 0            | 10  | 0            | 10  | ns      | 3, 6    |

| G High to Output High Z               |             | tGHQZ                   | 0            | 10  | 0            | 10  | ns      | 3, 6, 7 |

#### NOTES:

- A read is defined by W high for the specified setup and hold times.

- 2. A write is defined by W low for the specified setup and hold times.

- 3. All read and write cycle timing is referenced from K or from G.

- 4. Valid data from K high will be the data stored at the address of the last valid read cycle.

- 5. This is a synchronous device. All synchronous inputs must meet the specified setup and hold times with stable logic levels for ALL rising edges of clock (K) while the device is selected.

- 6. Transition is measured ±500 mV from steady-state voltage with load of Figure 1B. This parameter is sampled and not 100% tested. At any given voltage and temperature, t<sub>KHOZ</sub> max is less than t<sub>KHOZ</sub> min and t<sub>GHOZ</sub> max is less than t<sub>GLOX</sub> min for a given device.

7. \$\overline{G}\$ becomes a don't care signal for successive writes after the first write cycle.

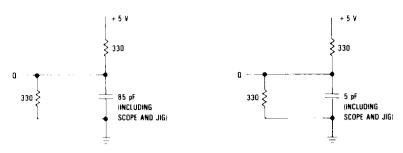

#### AC TEST LOADS

Figure 1A

Figure 1B

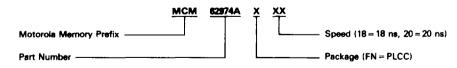

## ORDERING INFORMATION (Order by Full Part Number)

Full Part Numbers - MCM62974AFN18 MCM62974AFN20