### MC75450

## DUAL PERIPHERAL POSITIVE "AND" DRIVER

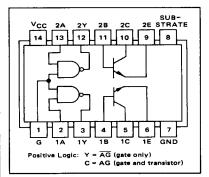

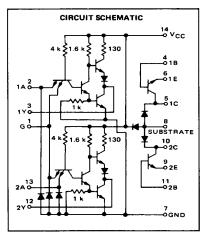

The MC75450 is a versatile device designed for use as a generalpurpose dual interface circuit in MDTL and MTTL type systems. This device features two standard MTTL gates and two noncommitted, high-current, high-voltage NPN transistors. Typical applications include relay and lamp drivers, power drivers, MOS and memory drivers.

- MDTL and MTTL Compatibility

- 300 mA Output Current Drive Capability (each transistor)

- Separate Gate and Output Transistor for Maximum Design Flexibility

- High Output Breakdown Voltage:

VCER = 30 Volts minimum

# DUAL PERIPHERAL POSITIVE "AND" DRIVER

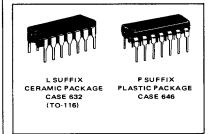

SILICON MONOLITHIC INTEGRATED CIRCUITS

#### MAXIMUM RATINGS (T<sub>A</sub> = 0 to +70°C unless otherwise noted)

| Rating                                                                                                               | Symbol           | Value       | Unit                     |

|----------------------------------------------------------------------------------------------------------------------|------------------|-------------|--------------------------|

| Power Supply Voltage (See Note 1)                                                                                    | Vcc              | +7.0        | Vdc                      |

| Input Voltage (See Note 1)                                                                                           | Vin              | 5.5         | Vdc                      |

| V <sub>CC</sub> -to-Substrate Voltage                                                                                |                  | 35          | Vdc                      |

| Collector-to-Substrate Voltage                                                                                       |                  | 35          | Vdc                      |

| Collector-Base Voltage                                                                                               | Vcв              | 35          | Vdc                      |

| Collector-Emitter Voltage (See Note 2)                                                                               | VCE              | 30          | Vdc                      |

| Emitter-Base Voltage                                                                                                 | VEB              | 5.0         | Vdc                      |

| Collector Current (continuous) (See Note 3)                                                                          |                  | 300         | mA                       |

| Power Dissipation (Package Limitation) Plastic and Ceramic Dual In-Line Packages Derate above T <sub>A</sub> = +25°C | PD               | 830<br>6.6  | mW<br>mW/ <sup>o</sup> C |

| Operating Temperature Range                                                                                          | TA               | 0 to +70    | °င                       |

| Storage Temperature Range                                                                                            | T <sub>stg</sub> | -65 to +150 | °c                       |

NOTES: 1. Voltage values are with respect to network ground terminal.

- This value applies when the base-emitter resistance (Rgg) is equal to or less than 500 ohms.

- Both halves of these dual circuits may conduct the rated current simultaneously.

#### RECOMMENDED OPERATING CONDITIONS (See Note 4)

| Characteristic | Symbol | Min  | Nom | Max  | Unit |

|----------------|--------|------|-----|------|------|

| Supply Voltage | vcc    | 4.75 | 5.0 | 5.25 | Vdc  |

Note 4. The substrate, pin 8, must always be at the most negative device voltage for proper operation.

#### ELECTRICAL CHARACTERISTICS (TA = 0 to +70°C unless otherwise noted.)

| Characteristic                                                                                                                                                   | Symbol          | Test Fig. | Min              | Тур*             | Max                    | Unit     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|------------------|------------------|------------------------|----------|

| MTTL GATES                                                                                                                                                       |                 |           |                  |                  |                        |          |

| High-Level Input Voltage                                                                                                                                         | ViH             | 1         | 2.0              | -                | -                      | Vdc      |

| Low-Level Input Voltage                                                                                                                                          | VIL             | 2         |                  | -                | 0.8                    | Vdc      |

| High-Level Output Voltage<br>(V <sub>CC</sub> = 4.5 V, V <sub>I</sub> L = 0.8 V, I <sub>OH</sub> = -400 μA)                                                      | Voн             | 2         | 2.4              | 3.3              | _                      | Vdc      |

| Low-Level Output Voltage ( $V_{CC}$ = 4.75 V, $V_{IH}$ = 2.0 V, $I_{OL}$ = 16 mA)                                                                                | VoL             | 1         | _                | 0.22             | 0.4                    | Vdc      |

| High-Level Input Current (V <sub>CC</sub> = 5.25 V, V <sub>in</sub> = 2.4 V) Input A Input G (V <sub>CC</sub> = 5.25 V, V <sub>in</sub> = 5.5 V) Input A Input G | ЦН              | 3         | -<br>-<br>-<br>- | _<br>_<br>_<br>_ | 40<br>80<br>1.0<br>2.0 | μA<br>mA |

| Low-Level Input Current (V <sub>CC</sub> = 5.25 V, V <sub>in</sub> = 0.4 V)                                                                                      | ήL              | 4         | -                | _<br>_           | -1.6<br>-3.2           | mA       |

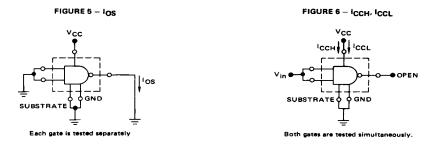

| Short-Circuit Output Current** (V <sub>CC</sub> = 5.25 V)                                                                                                        | los             | 5         | -18              | -                | -55                    | mA       |

| Supply Current High-Level Output (V <sub>CC</sub> = 5.25 V, V <sub>in</sub> = 0) Low-Level Output (V <sub>CC</sub> = 5.25 V, V <sub>in</sub> = 5.0 V)            | ICCH<br>ICCL    | 6         | _                | 2.0<br>6.0       | 4.0<br>11              | mA       |

| Input Clamp Voltage (V <sub>CC</sub> = 4.75 V, I <sub>in</sub> = -12 mA)                                                                                         | V <sub>in</sub> | 4         | -                | -                | -1.5                   | V        |

#### **OUTPUT TRANSISTORS**

| Characteristic                                                                                                                                                                                                                                                                                                                                                 | Symbol               | Min                  | Тур          | Max        | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|--------------|------------|------|

| Collector-Base Breakdown Voltage<br>(I <sub>C</sub> = 100 µA, I <sub>E</sub> = 0)                                                                                                                                                                                                                                                                              | VCBO                 | 35                   |              |            | Vdc  |

| Collector-Emitter Breakdown Voltage<br>(I <sub>C</sub> = 100 µA, R <sub>BE</sub> = 500 ohms)                                                                                                                                                                                                                                                                   | VCER                 | 30                   | -            | _          | Vdc  |

| Emitter-Base Breakdown Voltage<br>(I <sub>E</sub> = 100 µA, I <sub>C</sub> = 0)                                                                                                                                                                                                                                                                                | VEBO                 | 5.0                  | _            | _          | Vdc  |

| Static Forward Transfer Ratio (See Note 5)<br>(V <sub>CE</sub> = 3.0 V, I <sub>C</sub> = 100 mA, T <sub>A</sub> = +25°C)<br>(V <sub>CE</sub> = 3.0 V, I <sub>C</sub> = 300 mA, T <sub>A</sub> = +25°C)<br>(V <sub>CE</sub> = 3.0 V, I <sub>C</sub> = 100 mA, T <sub>A</sub> = 0°C)<br>(V <sub>CE</sub> = 3.0 V, I <sub>C</sub> = 300 mA, T <sub>A</sub> = 0°C) | μŁΕ                  | 25<br>30<br>20<br>25 | -<br>-<br>-  | -          |      |

| Base-Emitter Voltage (See Note 5)<br>(I <sub>B</sub> = 10 mA, I <sub>C</sub> = 100 mA)<br>(I <sub>B</sub> = 30 mA, I <sub>C</sub> = 300 mA)                                                                                                                                                                                                                    | VBE                  | -                    | 0.85<br>1.05 | 1.0<br>1.2 | Vdc  |

| Collector-Emitter Saturation Voltage (See Note 5) (I <sub>B</sub> = 10 mA, I <sub>C</sub> = 100 mA) (I <sub>B</sub> = 30 mA, I <sub>C</sub> = 300 mA)                                                                                                                                                                                                          | V <sub>CE(sat)</sub> |                      | 0.25<br>0.5  | 0.4<br>0.7 | Vdc  |

Note 5. These parameters must be measured using pulse techniques;  $t_W$  = 300  $\mu$ s, duty cycle  $\leq$  2%. \*All typical values at  $V_{CC}$  = 5.0 V,  $T_A$  = +25°C. \*\*Not more than one output should be shorted at a time.

#### SWITCHING CHARACTERISTICS (V<sub>CC</sub> = 5.0 V, T<sub>A</sub> = +25°C unless otherwise noted.)

| Characteristic                                                                                                                                                                           | Symbol         | Test Fig. | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------|-----|-----|-----|------|

| MTTL GATES                                                                                                                                                                               |                |           |     |     |     |      |

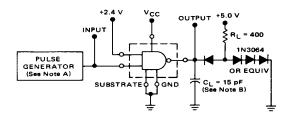

| Propagation Delay Time (C <sub>1</sub> = 15 pF, R <sub>L</sub> = 400 ohms)                                                                                                               |                | 7         |     |     |     | ns   |

| Low-to-High-Level Output                                                                                                                                                                 | l tPLH         |           | -   | 14  | _   |      |

| High-to-Low-Level Output                                                                                                                                                                 | <b>TPHL</b>    |           | _   | 6.0 | _   |      |

| OUTPUT TRANSISTORS #                                                                                                                                                                     |                |           |     |     |     |      |

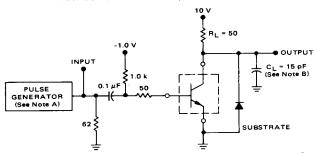

| Switching Times ( $I_C = 200 \text{ mA}$ , $I_{B(1)} = 20 \text{ mA}$ , $I_{B(2)} = -40 \text{ mA}$ , $V_{BE(off)} = -1.0 \text{ V}$ , $C_L = 15 \text{ pF}$ , $R_L = 50 \text{ ohms}$ ) |                | 8         |     |     |     | ns   |

| Delay Time                                                                                                                                                                               | td             |           | _   | 9.0 | _   |      |

| Rise Time                                                                                                                                                                                |                |           | _   | 11  | _   |      |

| Storage Time                                                                                                                                                                             | t <sub>r</sub> | 1         | _   | 14  | _   | 1    |

| Storage Time Fall Time                                                                                                                                                                   | t <sub>s</sub> | 1         |     | 8.0 |     |      |

|                                                                                                                                                                                          | tf             | <u> </u>  | L   |     | L   | L    |

| GATES AND TRANSISTORS COMBINED #                                                                                                                                                         |                |           |     |     |     |      |

| Propagation Delay Time (IC = 200 mA, CL = 15 pF, RL = 50 chms)                                                                                                                           |                | 9         | 1   |     |     | ns   |

| Low-to-High-Level Output                                                                                                                                                                 | tPLH           |           | -   | 21  | -   | ļ    |

| High-to-Low Level Output                                                                                                                                                                 | †PHL           |           | -   | 16  | -   |      |

| Transition Time # (IC = 200 mA, C <sub>1</sub> = 15 pF, R <sub>1</sub> = 50 ohms)                                                                                                        | 1              | 9         |     |     |     | ns   |

| Low-to-High-Level Output                                                                                                                                                                 | tTLH.          | 1         | -   | 7.0 | l – | 1    |

| High-to-Low-Level Output                                                                                                                                                                 | THL            | 1         | . – | 8.0 | -   | 1    |

<sup>&</sup>quot;Voltage and current values are nominal; exact values vary slightly with transistors parameters.

#### DC TEST CIRCUITS FOR MTTL GATES

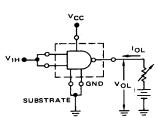

FIGURE 1 - VIH, VOL

Both inputs are tested simultaneously.

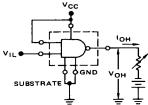

FIGURE 2 - VIL, VOH

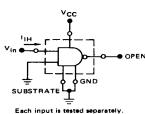

Each input is tested separately.

(Arrows indicate actual direction of current flow. Current into a terminal is a positive value.)

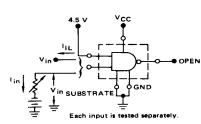

FIGURE 4 - I<sub>IL</sub>, V<sub>in</sub> FIGURE 3 - I<sub>IH</sub>

#### DC TEST CIRCUITS FOR MTTL GATES (continued)

(Arrows indicate actual direction of current flow. Current into a terminal is a positive value.)

FIGURE 7 - PROPAGATION DELAY TIMES, EACH GATE

NOTES: A. The pulse generator has the following characteristics:  $t_{\rm W}$  = 0.5  $\mu$ s, PRR = 1.0 MHz,  $z_{\rm O}$   $\approx$  50  $\Omega$ . B. C<sub>L</sub> includes probe and jig capacitance.

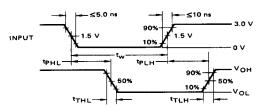

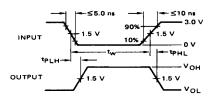

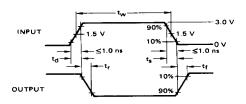

#### VOLTAGE WAVEFORMS

#### TEST CIRCUITS (continued)

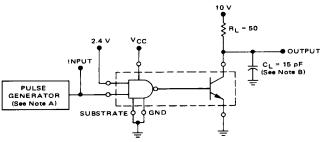

#### FIGURE 8 - SWITCHING TIMES, EACH TRANSISTOR

NOTES: A. The pulse generator has the following characteristics:  $t_W$  = 0.3  $\mu$ s, duty cycle  $\leq$  1%,  $z_0$   $\approx$  50  $\Omega$ . B. C<sub>L</sub> includes probe and jig capacitance.

#### VOLTAGE WAVEFORMS

#### FIGURE 9 - SWITCHING TIMES, GATE AND TRANSISTOR

NOTES: A. The pulse generator has the following characteristics:  $\tau_{\rm W}$  = 0.5  $\mu$ s, PRR = 1.0 MHz,  $z_{\rm O}$   $\approx$  50  $\Omega$ . B. C<sub>L</sub> includes probe and jig capacitance.

#### VOLTAGE WAVEFORMS