4028757 GOLDSTAR TECHNOLOGY INC.

04E 01650

T-45-23-21

# **GD4022B**

## 4-STAGE DIVIDE-BY-8 JOHNSON COUNTER

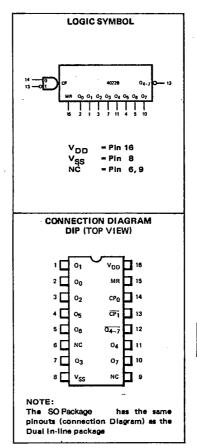

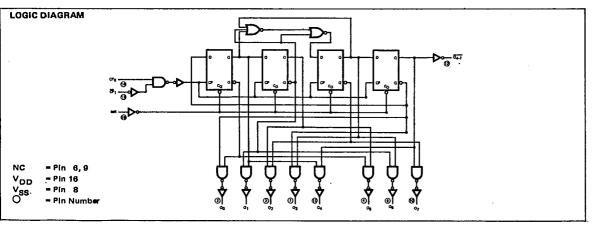

DESCRIPTION -- The 4022B is a 4-Stage Divide-by-8 Johnson Counter with eight glitch free active HIGH Decoded Outputs (O<sub>0</sub>-O<sub>7</sub>), an active LOW Output from the most significant flip-flop (O<sub>4-7</sub>), an active HIGH and an active LOW Clock Input (CPO, CP1) and an overriding asynchronous Master Reset Input (MR).

The counter is advanced by either a LOW-to-HIGH transition at CP $_0$  while  $\overline{\text{CP}_1}$  is LOW or a HIGH-to-LOW transition at  $\overline{\text{CP}_1}$  while CP $_0$  is HIGH (see Functional Truth Table). When cascading the counters, the  $\overline{\text{Q}_{4-7}}$  Output (which is LOW while the counter is in states 4, 5, 6 and 7) can be used to drive the CPo Input of the next 4022B, A HIGH on the Mester Reset Input (MR) resets the counter to Zero  $(O_0 = \overline{O_{4-7}} = HIGH, O_1 - O_7 = LOW)$  independent of the Clock Inputs (CP<sub>0</sub>,  $\overline{CP_1}$ ).

- CLOCK EDGE-TRIGGERED ON EITHER A LOW-TO-HIGH TRANSITION OR A **HIGH-TO-LOW TRANSITION**

- BUFFERED CARRY OUTPUT (04-7) AVAILABLE FOR CASCADING

- . BUFFERED FULLY DECODED OUTPUTS

### **PIN NAMES**

Clock Input (L→H Edge-Triggered) Clock Input (H-+L Edge-Triggered)

Master Reset Input

**Decoded Outputs** Carry (Active LOW) Output

#### **FUNCTIONAL TRUTH TABLE**

| MR | CP <sub>O</sub> | CP <sub>1</sub> | OPERATION                |

|----|-----------------|-----------------|--------------------------|

| Н  | Х               | Х               | 00 = 04-7 = H; 01-07 = L |

| L  | н               | H→L             | Counter Advances         |

| L  | L→H             | L               | Counter Advances         |

| L  | L               | ×               | No Change                |

| L  | х               | н               | No Change                |

| L  | н               | L→H             | No Change                |

| L  | L→L             | L               | No Change                |

= HIGH Level

- LOW Level

= LOW-to-HIGH Transition

H→L = HIGH-to-LOW Transition

X = Don't Care

. 75

04E 01651

DT-45.23-21

#### GS CMOS · GD4022B

| DC CHARACTERISTICS: VD | as shown, VSS = | 0 V (See Note 1) |

|------------------------|-----------------|------------------|

|------------------------|-----------------|------------------|

| SYMBOL          | PARAMETER  |    |                       | LIMITS |     |                        |     |     |                        |     |     |       |           |                        |

|-----------------|------------|----|-----------------------|--------|-----|------------------------|-----|-----|------------------------|-----|-----|-------|-----------|------------------------|

|                 |            |    | V <sub>DD</sub> = 5 V |        |     | V <sub>DD</sub> = 10 V |     |     | V <sub>DD</sub> = 15 V |     |     | UNITS | TEMP      | TEST CONDITIONS        |

|                 |            |    | MIN                   | TYP    | MAX | MIN                    | TYP | MAX | MIN                    | TYP | MAX |       |           |                        |

| I <sub>DD</sub> | Quiescent  | хс |                       |        | 20  |                        |     | 40  |                        |     | 80  | μА    | MIN, 25°C | All inputs at          |

|                 | Power      |    |                       |        | 150 |                        |     | 300 |                        |     | 600 |       | MAX       |                        |

|                 | Supply     |    |                       |        | 5   |                        | T   | 10  |                        |     | 20  |       | MIN, 25°C | 0 V or V <sub>DD</sub> |

|                 | Current XM |    |                       |        | 150 |                        |     | 300 |                        |     | 600 | μA    | MAX       |                        |

### AC CHARACTERISTICS AND SET-UP REQUIREMENTS: VDD as shown, VSS = 0 V, TA = 25°C (See Note 2)

| SYMBOL           | PARAMETER                                           | T                     |     | •   | UNITS | TEST CONDITIONS |                        |     |     |                        |          |                                             |

|------------------|-----------------------------------------------------|-----------------------|-----|-----|-------|-----------------|------------------------|-----|-----|------------------------|----------|---------------------------------------------|

|                  |                                                     | V <sub>DD</sub> = 5 V |     |     |       |                 | V <sub>DD</sub> = 10 V |     |     | V <sub>DD</sub> = 15 V |          |                                             |

|                  |                                                     | MIN                   | TYP | MAX | MIN   | TYP             | MAX                    | MIN | TYP | MAX                    | <u> </u> |                                             |

| <sup>t</sup> PLH | Propagation Delay,                                  |                       | 245 |     |       | 95              |                        |     | 60  |                        |          |                                             |

| tPHL.            | CPO or CP1 to On                                    |                       | 195 |     |       | 75              |                        |     | 50  |                        | ns       |                                             |

| tPLH             | Propagation Delay,                                  |                       | 190 |     |       | 75              |                        |     | 50  |                        |          |                                             |

| tPHL .           | CPO or CP1 to Q4-7                                  |                       | 245 | 1   |       | 90              |                        |     | 60  |                        | ns       |                                             |

| tPHL             | Propagation Delay, MR to On                         |                       | 130 |     |       | 55              |                        |     | 40  |                        | ns       |                                             |

| tPLH             | Propagation Delay, MR to Q4-7                       |                       | 110 |     |       | 45              |                        |     | 35  |                        | ns       | C <sub>L</sub> = 50 pF,                     |

| tTLH             | Contract Transition Time                            | 1                     | 70  |     |       | 35              |                        |     | 25  |                        | ns       | R <sub>L</sub> = 200 kΩ<br>Input Transition |

| <sup>t</sup> THL | Output Transition Time                              | 1                     | 70  |     |       | 35              |                        |     | 25  |                        |          |                                             |

| twCP             | Min. CP <sub>0</sub> or CP <sub>1</sub> Pulse Width |                       | 35  |     |       | 15              |                        |     | 10  |                        | ns       | Times < 20 ns                               |

| twMR             | Minimum MR Pulse Width                              | -                     | 35  |     |       | 15              |                        |     | 10  | L                      | ns       |                                             |

| trec             | MR Recovery Time                                    |                       | 10  |     | Γ     | 5               |                        |     | 5   |                        | ns       |                                             |

| th               | Hold Time, CP <sub>0</sub> to CP <sub>1</sub>       |                       | 70  |     |       | 25              |                        |     | 15  |                        | П\$      |                                             |

| th               | Hold Time, CP <sub>1</sub> to CP <sub>0</sub>       | 1                     | 85  |     |       | 30              |                        |     | 20  |                        | ns       |                                             |

| f <sub>MAX</sub> | Input Count Frequency (Note 3)                      |                       | 6   |     |       | 16              |                        |     | 24  |                        | MHz      |                                             |

NOTES:

Additional QC Characteristics are listed in this section under 4000B Series CMOS Family Characteristics.

Propagation Delays and Output Transition Times are graphically described in this section under 4000B Series CMOS Family Characteristics.

For f<sub>MAX</sub>, input rise and fall times are greater than or equal to 5 ns and less than or equal to 20 ns.

It is recommended that input rise and fall times to the Clock Input be less than 15 μs at V<sub>DD</sub> = 5 V, 4 μs at V<sub>DD</sub> = 10 V, and 3 μs at V<sub>DD</sub> = 15 V.

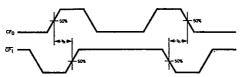

## HOLD TIMES, CPO TO CP1 AND CP1 TO CPO

NOTE: Note: Hold Times are shown as positive values, but may be specified as negative values.

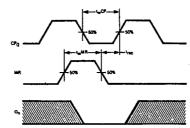

$\begin{array}{c} \textbf{MINIMUM PULSE WIDTHS FOR CP AND MR} \\ \textbf{AND RECOVERY TIME FOR MR} \\ \textbf{CONDITIONS:}\overline{CP_1} = \texttt{LOW} \text{ while } CP_0 \text{ is triggered on a LOW-to-HIGH transition.} \\ \textbf{t}_w CP \text{ and } \textbf{t}_{rec} \text{ also apply when } CP_0 = \texttt{HIGH and } \overline{CP_1} \text{ is triggered on a HIGH-to-LOW transition.} \end{array}$