# 41MG and 41MP Quad Differential Line Drivers

#### **Features**

- Pin-equivalent to the general-trade 26LS31 device, with improved speed, reduced power consumption, and significantly lower levels of EMI

- Four line drivers per package

- Logic which converts TTL input logic levels to differential, pseudo-ECL output logic levels

- 200 Mbits/s or 400 Mbits/s maximum data rates when used with the 41Lx and 41Mx receivers respectively

- Meets ESDI standards

- No line loading when Vcc = 0 V

- $\blacksquare$  High output drive for 50  $\Omega$  lines

- 200 mA short-circuit current (typical)

- 2 ns maximum propagation delay

- <0.2 ns output skew (typical)</p>

- 0 °C to 85 °C ambient operating temperature range (See Section 9.)

- Single 5 V supply

## **Description**

The 41MG and 41MP Quad Differential Line Driver integrated circuits transmit digital data over balanced transmission lines. They translate input TTL levels to differential, pseudo-emitter-coupled logic (pseudo-ECL) output levels. All devices in this family have four drivers with a common enable control. The 41MG and 41MP line drivers are compatible with many receivers, including the AT&T 41 Series receivers and transceivers and the general-trade 26LS32 device. The 41MG devices require the customer to supply external termination resistors on the circuit board. The 41MP devices have internal 220  $\Omega$  termination resistors to ground on each driver output. The 41MG/41MP drivers are pin-equivalent to the general-trade 26LS31 devices but offer increased speed, reduced power consumption, and significantly lower levels of electromagnetic interference (EMI).

The packaging options that are available for the quad differential line drivers include a 16-pin DIP (41MG, 41MP), a 16-pin J-lead SOJ (1041MG, 1041MP), a 16-pin gull-wing SOIC (1141MG, 1141MP), and a 16-pin narrow-body gull-wing SOIC (1241MG).

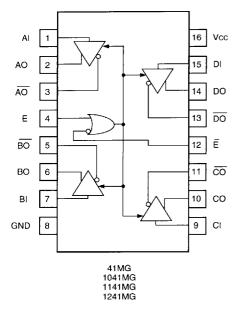

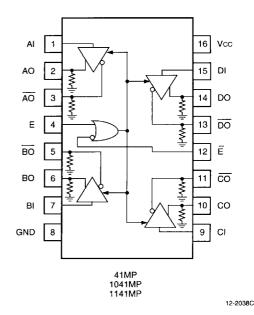

#### Pin Information

Note: The device is disabled when E = 0 and  $\overline{E} = 1$ .

Figure 3-3. 41MG and 41MP Logic Diagrams

## **Absolute Maximum Ratings**

Stresses in excess of the Absolute Maximum Ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to Absolute Maximum Ratings for extended periods can adversely affect device reliability.

| Parameter                     | Symbol | Min | Max | Unit |

|-------------------------------|--------|-----|-----|------|

| Power Supply Voltage          | Vcc    |     | 7.0 | V    |

| Ambient Operating Temperature | TA     | 0   | 85  | °C   |

| Storage Temperature           | Tstg   | -40 | 125 | °C   |

# **Handling Precautions**

CAUTION: This device is susceptible to damage as a result of electrostatic discharge. Take proper precautions during both handling and testing. Follow guidelines such as JEDEC Publication No. 108-A (Dec. 1988).

AT&T employs a human-body model (HBM) for ESDsusceptibility testing and protection-design evaluation. 3-10 ESD voltage thresholds are dependent on the critical parameters used to define the model. The standard HBM (resistance = 1.5 k $\Omega$ , capacitance = 100 pF) is used. The HBM ESD threshold voltage presented here was obtained using this circuit.

| Device            | Rating  |  |  |

|-------------------|---------|--|--|

| 41MG/41MP Drivers | >1000 V |  |  |

#### **Electrical Characteristics**

Table 3-7. 41MG and 41MP Power Supply Current Characteristics

Ta = 0  $^{\circ}$ C to 85  $^{\circ}$ C, Vcc = 5 V  $\pm$  0.5 V.

| Parameter             | Symbol | Min | Тур | Max | Unit |

|-----------------------|--------|-----|-----|-----|------|

| Power Supply Current: |        |     |     |     |      |

| 41MG*                 |        |     |     |     |      |

| All Outputs Disabled  | lcc    | _   | 60  | 90  | mA   |

| All Outputs Enabled   | Icc    |     | 35  | 55  | mA   |

| 41MP <sup>†</sup>     |        |     |     |     |      |

| All Outputs Disabled  | Icc    | _   | 130 | 180 | mA   |

| All Outputs Enabled   | lcc    | _   | 160 | 230 | mA   |

Measured with no load

### Table 3-8. 41MG and 41MP Voltage and Current Characteristics

$T_A = 0$  °C to 85 °C.

| Parameter                                 | Symbol            | Min  | Тур  | Max                    | Unit |

|-------------------------------------------|-------------------|------|------|------------------------|------|

| Output Voltages, Vcc = 4.5 V:             |                   |      |      |                        |      |

| Low, $IoL = -8.0 \text{ mA}^*$            | Vol               | _    | 3.0  | Vон – 0.8 <sup>†</sup> | V    |

| High, loн = $-40.0 \text{ mA}^*$          | Vон               | 3.0  | 4.0  | _                      | V    |

| High Z, lон = −1.0 mA, Vcc = 4.75 V       | Voz               | _    | 2.0  | Vol - 0.02             | V    |

| Input Voltages:                           |                   |      |      |                        |      |

| Low, Vcc = 5.5 V                          | Vı∟‡              | _    | _    | 0.8                    | V    |

| High, Vcc = 4.5 V                         | V <sub>IH</sub> ‡ | 2.0  |      |                        | V    |

| Clamp, Vcc = 4.5 V, IiN = -5.0 mA         | Vik               | _    |      | -1.5                   | V    |

| Short-circuit Output Current, Vcc = 5.5 V | los§              | -100 | -250 | -350                   | mA   |

| Input Currents, Vcc = 5.5 V:              |                   |      |      |                        |      |

| Low, VIN = 0.4 V                          | hL                | -    | _    | -400                   | μΑ   |

| High, Vin = 2.7 V                         | lін               | _    | _    | 20                     | μΑ   |

| Reverse, Vin = 5.5 V                      | lı∺               | _    | _    | 100                    | μΑ   |

| Output Resistors (41MP)                   | Ro                | _    | 220  | _                      | Ω    |

<sup>\*</sup> Typical value of the output current for the 41LG and the 41MP when terminated per Figure 6-5

<sup>†</sup> The additional power dissipation is the result of integrating the termination resistors into the device. Icc is measured with a 100 Ω resistor across the driver outputs

$<sup>^\</sup>dagger$  Vol. must be a minimum of 0.8 V less than its complementary output for Vcc MIN = 4.75 V

<sup>&</sup>lt;sup>‡</sup> The input levels provide zero noise immunity and should be tested only in a static, noise-free environment

<sup>§</sup> Test must be performed one lead at a time to prevent damage to the device

# **Timing Characteristics**

Table 3-9. 41MG and 41MP Timing Characteristics (See Figures 6-1 and 6-2.)

Propagation-delay test circuit connected to output (see Figure 6-6).

$T_A = 25$  °C,  $V_{CC} = 5$  V.

| Symbol          | Parameter                    | Тур | Max | Unit |

|-----------------|------------------------------|-----|-----|------|

|                 | Propagation Delay:           |     |     |      |

| tP1             | Input High to Output         | 1.0 | 2.0 | ns   |

| tp2             | Input Low to Output          | 1.0 | 2.0 | ns   |

|                 | Disable Time:                |     |     |      |

| tpHZ            | High to High Impedance       | 8   | 12  | ns   |

| <b>t</b> PLZ    | Low to High Impedance        | 8   | 12  | ns   |

| -               | Enable Time:                 |     |     |      |

| tpzh            | High Impedance to High       | 8   | 12  | ns   |

| <b>t</b> PZL    | High Impedance to Low        | 8   | 12  | ns   |

| tskew1          | ltp1 - tp2l                  | 0.2 | 0.5 | ns   |

| tskew2          | ltpнн — tpнLl, ltpLн — tpLLl | 0.9 | 1.2 | ns   |

| $\Delta t$ skew | Difference Between Drivers   | 0.3 | 0.6 | ns   |

| tıLH            | Rise Time                    | _   | 2.0 | ns   |

| tıHL            | Fall Time                    | _   | 2.0 | ns   |

3-12