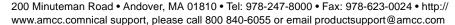

The Hudson is a fully integrated, Variable Rate Digital Wrapper Framer/Deframer, Performance Monitor, and Forward Error Correction (FEC) device supporting the Digital Wrapper transmission standards for OTU1, OTU2, ODU1, ODU2, OPU1, and OPU2 as specified in G.709. The Hudson implements Performance Monitoring and overhead processing functions on the Digital Wrapper overhead bytes. In addition, the device contains SONET/SDH Performance Monitoring to verify the validity of the SONET/SDH OC-192 client data. The device can operate from a low rate of 6.25 MHz to a high rate of 693.483 MHz. Data entering and leaving the chip can be optionally deframed and framed, descrambled and scrambled, and decoded and encoded with forward error correction information.

- Core logic runs on a 1.8 V power supply to reduce power consumption and LVCMOS I/O are 3.3 V compatible.

- Two independent 16-bit parallel LVDS input and output ports at up to 693.483 MHz (11.096 Gbps).

- Datapath options: Configurable as two completely independent data stream for full duplex operation. Configurable as a single data stream for regenerator operation with dual redundant I/O for optional protection switching. Either input port can be directly connected to either output port for loopback testing or bypass operation.

- Supports SONET OC-192 Performance Monitoring at the input of the encoder side and at the output of the decoder side.

- Supports G.709 "Interfaces for the optical transport network (OTN)" standard including specified frame structure, all overhead monitoring and processing, Maintenance signals, synchronous and asynchronous mapping and demapping.

- ON/OFF control of Reed-Solomon (255,239) FEC Encoding/ Decoding and error correction.

- Support for System test and diagnostics: internal BER generator, PRBS pattern generator and pattern analyzer for bit error rate testing capability.

- Four programmable integer clock dividers to simplify clock generation.

- Support for signal aggregation to higher rates via chip synchronization feature.

- General Purpose Processor Interface: Gluess interface to MPC860, 25 MHz to 50 MHz bus speed. Also compatible with Intel microprocessor bus via Busmode selector.

- · Low power: 0.18 micron CMOS technology.

### **Applications**

- 10 Gigabit Digital Wrapper Performance Monitor and Framer

- Protocol Independent DWDM Metropolitan Area Networks

- Optical Cross-connects

- OC-192 Port interface

- · Fiber optic terminators, repeaters, and test equipment

Figure 1: Block Diagram

# **General Description**

### **Operating Frequencies**

Digital Wrapper functionality is available on the Hudson without regard to the actual data rate. The table below shows the supported frequencies of operation for Digital Wrapper transponder and SONET/SDH monitoring applications. Note that SONET/SDH monitoring is only supported for the OC-192 rate.

| Mode                          | Frequency (Data Rate)                                            |

|-------------------------------|------------------------------------------------------------------|

| Digital<br>Wrapper            | 6.25 MHz (100 Mbps) to 693.483<br>MHz (11.096 Gbps) <sup>1</sup> |

| SONET/<br>SDH Moni-<br>toring | 622.08 MHz (9.95 Gbps) ONLY                                      |

<sup>1.</sup> Note: G.709 specifies exact rates for the Digital Wrapper. At the OTU2 rate, the frequency of the Hudson data ports is 669.33 MHz. The Hudson can be safely run at lower rates than specified in G.709 if compatibility to the standard is not required.

#### **Typical Full Duplex Application**

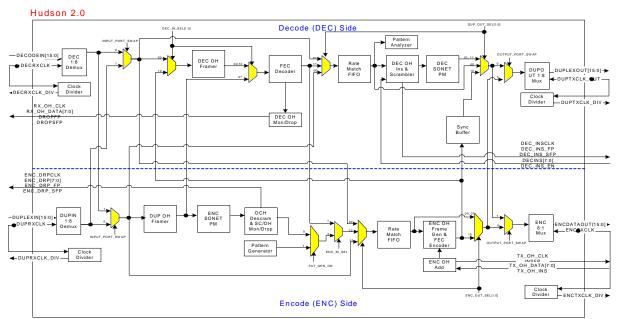

In the Full-Duplex configuration, the encode side and decode side of the Hudson can operate independently as shown below. At the input to the encode side of the Hudson is a SONET monitor which can verify the integrity of the SONET data stream prior to wrapping and FEC. At the output of the decode side, another SONET monitor

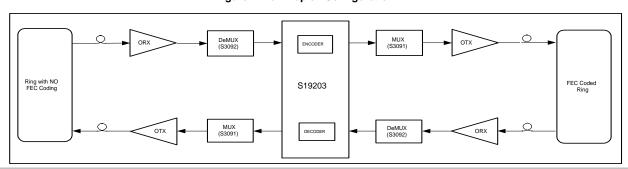

exists after decoding and deframing, to verify the integrity of the wrapper's SONET payload before it exits the Hudson. Wrapper overhead insertion and extraction, encoding and decoding, and performance monitoring are carried out on the output and input data streams respectively. The Hudson also contains many features to help the user with device integration and line testing. The Hudson high speed I/O is also compatible with the AMCC SONET/SDH Mapper or Interleaver/Disinterleaver. A typical edge application is shown below.

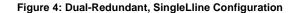

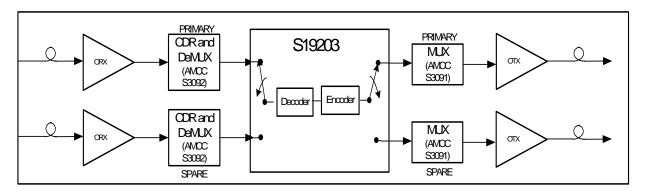

## **Typical Single-line Application**

The following figures also illustrate a typical network application for the Hudson supporting a single data stream with dual redundant input and output lines. This configuration is useful for core transponder applications where it is desired to correct errors and do performance monitoring and output a corrected and FEC encoded data stream with or without new Optical Channel Overhead (Digital Wrapper OH) bytes. Data is received from the fiber and passed through a Clock/Data Recovery device (CDR) and a demultiplexer device to the Hudson. The Hudson optionally carries out SONET/ SDH monitoring, digital wrapper performance monitoring, error checking, and overhead data extraction and insertion. Detected errors and accumulated error counts can be accessed by the user either through a processor interface, an FPGA interface, or in a number of cases, from I/O pins. The data stream is then transmitted out onto the fiber via a high-speed multiplexer and an optics device. FEC decoding and encoding may be disabled individually.

Figure 2: Full-Duplex Configuration

Figure 3: Typical Edge Application

Part Number S19203CBI20, Revision 1.3, May 2003

Figure 5: Se;f-Healing BLSR FEC Encoded Network

AMCC reserves the right to make changes to its products, or to discontinue any product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied upon is current.

AMCC is a registered trademark of Applied Micro Circuits Corporation. Copyright © 2002 Applied Micro Circuits Corporation. All Rights Reserved.