#### LG1627BXC Clocked Laser Driver

#### **Features**

- High data-rate clocked laser diode driver

- Clock disable mode for data feedthrough

- Adjustable high output current

- Operation up to 3 Gbits/s

#### **Applications**

- SONET/SDH transmission systems

- SONET/SDH test equipment

- Optical transmitters

#### **Functional Description**

The LG1627BXC is a gallium arsenide (GaAs) laser diode driver to be used with direct modulated laser diodes in high-speed non-return-to-zero (NRZ) transmission systems. The device is made in a highperformance 0.9 µm gate GaAs hetero-junction FET technology that utilizes high-density MIM capacitors, airbridge interconnect, and NiCr film precision resistors. The driver includes differential data and clock inputs. The high-output, low overshoot drive current and prebias can be set separately. Data retiming is accomplished by the internal flip-flop, minimizing jitter on the data. Clocking can be disabled for data feedthrough. A pulse-width control enables the user to compensate for laser turn-on delay. A 2.5 V bandgap reference is required for stable operation over temperature and varying power supply voltage.

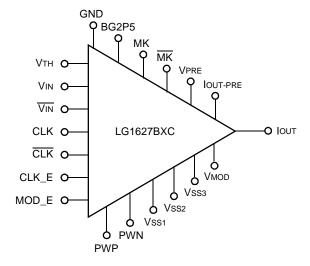

#### **Functional Diagram**

5-6549(F).b

Figure 1. Functional Diagram

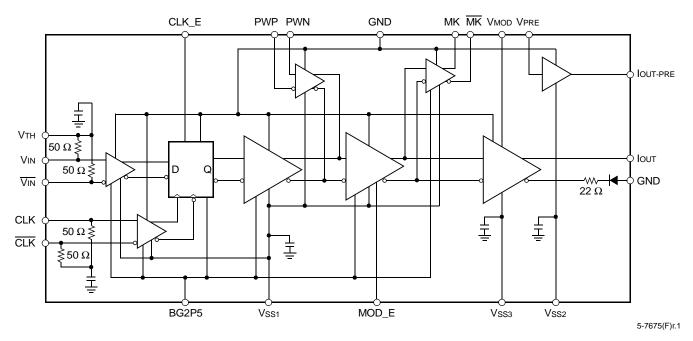

# **Block Diagram**

Figure 2. Block Diagram

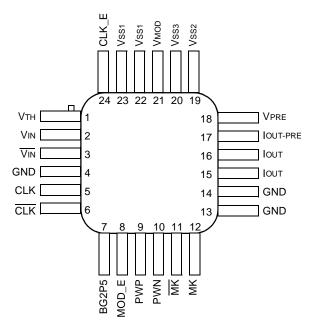

#### **Pin Information**

Figure 3. Pin Diagram

**Table 1. Pin Descriptions**

| Pin                             | Symbol   | Description                                                                               |

|---------------------------------|----------|-------------------------------------------------------------------------------------------|

| 1                               | VTH      | Capacitor to ground (data input reference).                                               |

| 2                               | VIN      | Data input.                                                                               |

| 3                               | VIN      | Complementary data input.                                                                 |

| 4, 13, 14,<br>package<br>bottom | GND      | Ground. For optimum performance, the package bottom must be soldered to the ground plane. |

| 5                               | CLK      | Clock input.                                                                              |

| 6                               | CLK      | Complementary clock input.                                                                |

| 7                               | BG2P5    | -2.5 V band-gap reference (National Semiconductor* p/n LM4040).                           |

| 8                               | MOD_E    | Modulation enable (connect to VSS1 to enable, float to disable).                          |

| 9                               | PWP      | Pulse width adjust positive.                                                              |

| 10                              | PWN      | Pulse width adjust negative.                                                              |

| 11                              | MK       | Complementary mark density output.                                                        |

| 12                              | MK       | Mark density output.                                                                      |

| 15, 16                          | lout     | Output modulation current (dc coupled to laser cathode).                                  |

| 17                              | IOUT-PRE | Output prebias current.                                                                   |

| 18                              | VPRE     | Prebias control input.                                                                    |

| 19                              | VSS2     | VSS2 supply −5.2 V for output prebias.                                                    |

| 20                              | Vss3     | VSS3 supply –5.2 V for output modulation.                                                 |

| 21                              | VMOD     | Modulation current control input.                                                         |

| 22, 23                          | VSS1     | VSS1 supply −5.2 V.                                                                       |

| 24                              | CLK_E    | Clock enable (connect to VSS1 to enable, float to disable).                               |

<sup>\*</sup> National Semiconductor is a registered trademark of National Semiconductor Corporation.

Agere Systems Inc.

3

5-6551(F).br.3

#### **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

**Table 2. Absolute Maximum Ratings**

| Parameter                        | Symbol | Min | Max  | Unit |

|----------------------------------|--------|-----|------|------|

| Supply Voltage                   | Vss    | _   | -5.7 | V    |

| Input Voltage                    | Vı     | GND | Vss  | V    |

| Power Dissipation                | PD     | _   | 1    | W    |

| Storage Temperature              | Tstg   | -40 | 125  | °C   |

| Operating Case Temperature Range | Tc     | 0   | 100  | °C   |

#### **Recommended Operating Conditions**

**Table 3. Recommended Operating Conditions**

| Parameter        | Symbol | Min  | Max  | Unit |

|------------------|--------|------|------|------|

| Case Temperature | tCASE  | 0    | 70   | °C   |

| Power Supply     | Vss    | -4.7 | -5.7 | V    |

### **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Lucent employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used to define the model. No industry-wide standard has been adopted for the CDM. However, a standard HBM (resistance =  $1500~\Omega$ , capacitance = 100~pF) is widely used and, therefore, can be used for comparison. The HBM ESD threshold presented here was obtained by using these circuit parameters.

Table 4. ESD Threshold Voltage

| Human-Body Model ESD Threshold |         |  |  |  |

|--------------------------------|---------|--|--|--|

| Device                         | Voltage |  |  |  |

| LG1627BXC                      | >200    |  |  |  |

### **Mounting and Connections**

Certain precautions must be taken when using solder. For installation using a constant temperature solder, temperatures of under 300 °C may be employed for periods of time up to 5 seconds, maximum. For installation with a soldering iron (battery operated or nonswitching only), the soldering tip temperature should not be greater than 300 °C and the soldering time for each lead must not exceed 5 seconds. This device is supplied with solder on the back of the package. For optimum performance, it is recommended to solder the back of the package to ground.

Electrical Characteristics (TA = 25 °C, VSS1 = VSS2 = VSS3 = -5.2 V, data input = 600 mV (single ended), and RL =  $50 \Omega$ )

Minimum and maximum values are testing requirements. Typical values are characteristics of the device and are the result of engineering evaluations. Typical values are for information purposes only and are not part of the testing requirements. Stresses in excess of the absolute maximum ratings can cause permanent damage to the device.

**Table 5. Electrical Characteristics**

| Parameter                                             | Symbol                                        | Min  | Тур  | Max  | Unit |  |

|-------------------------------------------------------|-----------------------------------------------|------|------|------|------|--|

| Data Input Voltage, Single Ended                      | VIN                                           | 300  | 600  | 1000 | mV   |  |

| Power Supply Voltage                                  | VSS1, VSS2, VSS3                              | -4.9 | -5.2 | -5.5 | V    |  |

| Power Supply Current <sup>1</sup>                     | ISS1                                          | 100  | 140  | 160  | mA   |  |

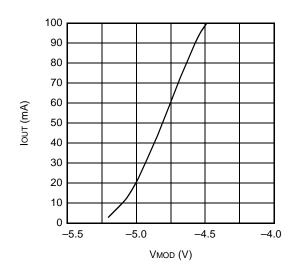

| Voltage Control for Output Modulation Current         | VMOD                                          | -4.0 | _    | -5.5 | V    |  |

| Output Minimum Modulation Current                     | IOUT LOW                                      | _    | 0    | 2    | mA   |  |

| Output Maximum Modulation Current <sup>2</sup>        | IOUT HIGH                                     | 75   | 85   | _    | mA   |  |

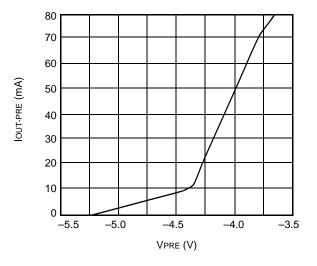

| Voltage Control for Prebias Current                   | VPRE                                          | -3.0 | _    | -5.5 | V    |  |

| Output Minimum Prebias Current                        | IPRE LOW                                      | _    | 0    | 0.5  | mA   |  |

| Output Maximum Prebias Current <sup>3</sup>           | IPRE HIGH                                     | 50   | 60   | _    | mA   |  |

| Mark Density, 50% Duty Cycle (1 kΩ to GND)            | MK                                            | _    | -0.5 | _    | V    |  |

| Mark Density Complement, 50% Duty Cycle (1 kΩ to GND) | MK                                            | _    | -0.5 | _    | V    |  |

| Pulse Width Adjust Plus                               | PWP                                           | -3.0 | -4.2 | -5.5 | V    |  |

| Pulse Width Adjust Negative                           | PWN                                           | -3.0 | -4.2 | -5.5 | V    |  |

| Output Modulation IouT = 40 mA, Clock Enabl           | Output Modulation Iout = 40 mA, Clock Enabled |      |      |      |      |  |

| Output Rise and Fall Times (20%—80%)                  | tR, tF                                        | _    | 90   | _    | ps   |  |

| Jitter (rms)                                          | _                                             | _    | 4    | _    | ps   |  |

| Phase Margin                                          | _                                             | _    | 270  | _    | deg  |  |

| Output Modulation Iout = 40 mA, Clock Disabled        |                                               |      |      |      |      |  |

| Output Rise and Fall Times (20%—80%)                  | tR, tF                                        | _    | 90   | _    | ps   |  |

| Jitter (rms)                                          | _                                             | _    | 6    | _    | ps   |  |

| Output Modulation IOUT = 80 mA, Clock Enabled         |                                               |      |      |      |      |  |

| Output Rise and Fall Times (20%—80%)                  | tR, tF                                        | _    | 100  | _    | ps   |  |

| Jitter (rms)                                          | _                                             | _    | 4    | _    | ps   |  |

| Phase Margin                                          | _                                             | _    | 270  | _    | deg  |  |

| Output Modulation Iout = 80 mA, Clock Disabled        |                                               |      |      |      |      |  |

| Output Rise and Fall Times (20%—80%)                  | tR, tF                                        | _    | 100  | _    | ps   |  |

| Jitter (rms)                                          | _                                             | _    | 6    | _    | ps   |  |

<sup>1.</sup> Excludes IPRE and average IMOD.

Power supply current ISS2 (relating to prebias) is dependent on VPRE. Power supply current Iss3 (relating to modulation) is dependent on VMOD.

<sup>2.</sup> Maximum modulation at maximum VMOD.

<sup>3.</sup> Maximum prebias at maximum VPRE.

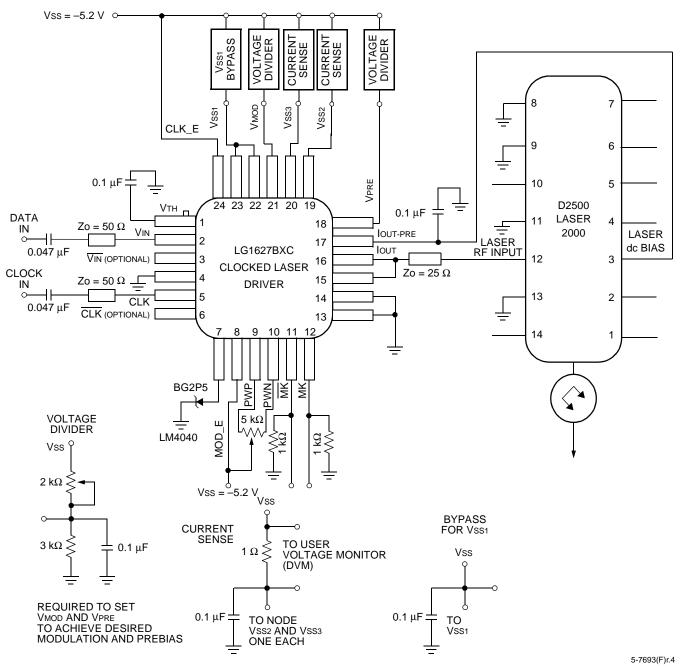

## **Typical Optical Evaluations and Performance Characteristics**

#### Notes:

All bypass capacitors should be mounted close to the package.

For optimum performance, the package must be soldered to ground.

Mark density (MK and  $\overline{\text{MK}}$ ) outputs are terminated with 1 k $\Omega$  pull-up resistors.

For single-ended operation, unused data and clock inputs should be ac coupled to a 50  $\Omega$  termination.

Pin 13 and pin 14 should be tied together with a separate path to the ground plane.

Figure 4. Typical Optical Evaluation of the LG1627BXC and D2500 Laser

# Typical Optical Evaluations and Performance Characteristics (continued)

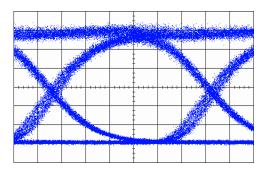

HORIZONTAL: 60 ps/div, VERTICAL: 1.5 mW/div

Figure 5. Typical Optical Eye-Diagram IouT = 85 mA; IouT-PRE = 5 mA

Figure 6. Typical lout vs. VMOD

5-7677(F)r.1

Figure 7. Typical IOUT-PRE vs. VPRE

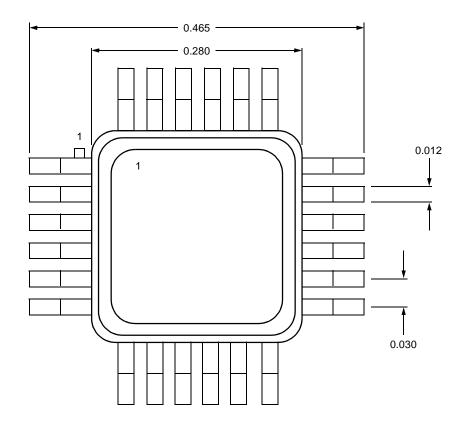

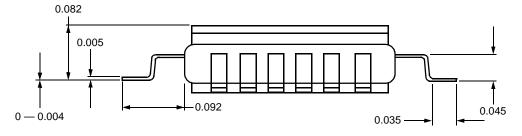

# **Outline Diagram**

5-6555(F).a

#### **Assembly Notes:**

Standoff specifications apply to package prior to solder dipping of leads and package base.

During board assembly, use back lighting to silhouette the package. This will eliminate reflection problems with the solder on the bottom of the package.

Lead space tolerance should be set to ±0.012".

Board solder pattern for the package base should not exceed 50% of the package base area.

Insertion pressure should not exceed 125 grams.

# **Ordering Information**

| Device Code | Package                       | Temperature   | Comcode<br>(Ordering Number) |

|-------------|-------------------------------|---------------|------------------------------|

| LG1627BXC   | 24-pin hermetic small outline | 0 °C to 70 °C | 108325754                    |

# **Notes**

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET: http://www.agere.com

E-MAIL: docmaster@micro.lucent.com

N. AMERICA: Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA PACIFIC: Agere Systems Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

CHINA: Agere Systems (Shanghai) Co., Ltd., 33/F Jin Mao Tower, 88 Century Boulevard Pudong, Shanghai 200121 PRC

Tel. (86) 21 50471212, FAX (86) 21 50472266

Agere Systems Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700

Data Requests: DATALINE: Tel. (44) 7000 582 368, FAX (44) 1189 328 148 JAPAN:

EUROPE:

Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot), FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 3507670 (Helsinki),

ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.