## Am7204A

# Advanced Micro Devices

# High Density First-In First-Out (FIFO) 4096 x 9-Bit CMOS Memory

#### **DISTINCTIVE CHARACTERISTICS**

- RAM based FIFO

- 4096 x 9 organization

- Cycle times of 25/35/45/65 ns for standard products

- Cycle times of 40/65 ns for APL products

- Asynchronous and simultaneous writes and reads

- Low power consumption

- Status flags—full, half-full, empty

- Retransmit capability

- Expandable in both width and depth

- Increased noise immunity for XI—CMOS threshold

- Functional and pin compatible with industry standard devices

#### **GENERAL DESCRIPTION**

The Am7204A is a RAM-based CMOS FIFO that is 4096 words deep with 9-bit wide words. It is expandable to any width and/or depth to create much larger FIFOs.

This FIFO can input and output data asynchronously and simultaneously at data rates from 0 to 40 MHz for Standard Products and 0 to 25 MHz for APL products. Status flags are provided to signify empty, full and half-

full conditions. The capability also exists to retransmit data from the FIFO.

High-density FIFOs such as the Am7204A are useful in a wide range of applications. The ability to buffer large transfers of data and the rate adaption capabilities make the Am7204A useful in communication, image processing, mass storage, DSP, and printing systems.

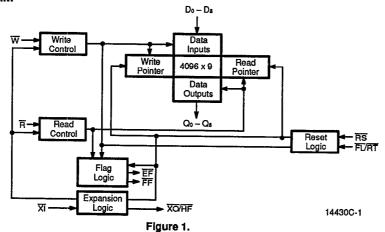

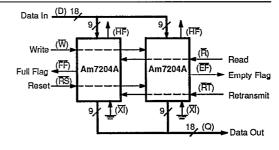

#### **BLOCK DIAGRAM**

PRODUCT SELECTOR GUIDE

| Part Number                     | Am7204A-15 | Am7204A-25 | Am7204A-35 | Am7204A-50 | Am7204A-30 | Am7204A-50 |

|---------------------------------|------------|------------|------------|------------|------------|------------|

| Access Time                     | 15 ns      | 25 ns      | 35 ns      | 50 ns      | 30 ns      | 50 ns      |

| Maximum Power<br>Supply Current | 90 mA      | 70 mA      | 60 mA      | 60 mA      | 100 mA     | 90 mA      |

| Operating<br>Frequency          | 40 MHz     | 28.5 MHz   | 22.2 MHz   | 15.3 MHz   | 25 MHz     | 15.3 MHz   |

| Operating Range                 | Com'l      | Com'l      | Com'l      | Com'l      | Mil        | Mil        |

Publication# 14430 Rev. C Amendment/0 Issue Date: September 1992

2-75

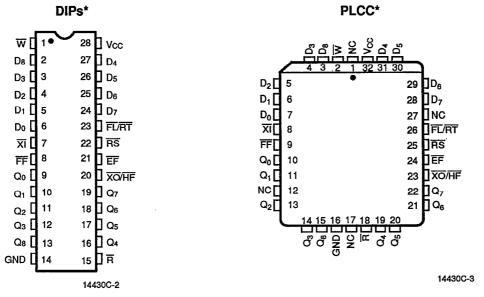

# CONNECTION DIAGRAMS Top View

#### Notes:

Pin 1 is marked for orientation for plastic packages.

\*Pinout identical for both plastic and ceramic DIPs.

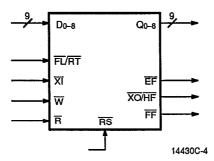

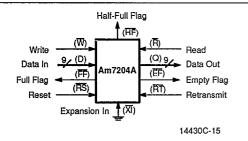

## **LOGIC SYMBOL**

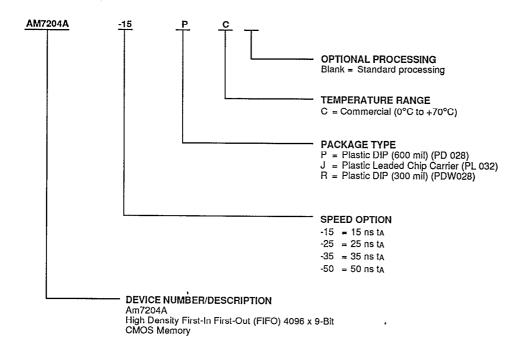

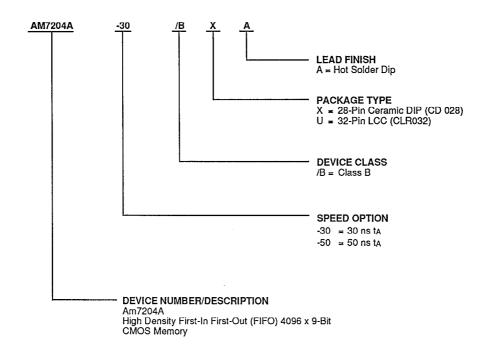

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Cor  | Valid Combinations |  |  |  |  |  |  |  |

|------------|--------------------|--|--|--|--|--|--|--|

| AM7204A-15 | RC, JC             |  |  |  |  |  |  |  |

| AM7204A-25 |                    |  |  |  |  |  |  |  |

| AM7204A-35 | PC, RC, JC         |  |  |  |  |  |  |  |

| AM7204A-50 |                    |  |  |  |  |  |  |  |

## Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, and to check on newly released valid combinations.

# MILITARY ORDERING INFORMATION APL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |            |  |  |  |  |  |  |

|--------------------|------------|--|--|--|--|--|--|

| AM7204A-30         | /DVA /DUA  |  |  |  |  |  |  |

| AM7204A-50         | /BXA, /BUA |  |  |  |  |  |  |

## Military Burn-In

Military burn-in is in accordance with the current revision of MIL-STD-883, Test Method 1015, Conditions A through E. Test conditions are selected at AMD's option.

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, or to check on newly released combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

#### Data In (Inputs (9))

These nine pins are the data inputs to the FIFO.

#### Empty Flag (Output; Active LOW)

The HIGH state of the Empty Flag (EF) indicates that the FIFO contains data to be read. The EF goes LOW when the read pointer is equal to the write pointer, indicating that the device is empty. EF LOW inhibits further Read operations.

The  $\overline{\mathsf{EF}}$  goes HIGH after the rising edge of Write ( $\overline{\mathsf{W}}$ ) during the first write cycle for an empty FIFO (See Figure 4). The EF goes LOW after the falling edge of Read (R) during the read cycle which creates the empty condition.

During a Reset cycle, the EF is driven LOW (active).

#### Full Flag (Output; Active LOW)

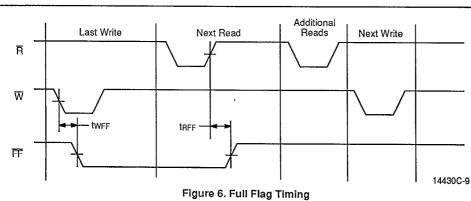

The HIGH state of the Full Flag ( $\overline{\text{FF}}$ ) indicates that the FIFO is capable of accepting data. The  $\overline{\text{FF}}$  goes LOW when the write pointer is one location less than the read pointer, indicating that the device is full. FF LOW inhibits further Write operations.

The  $\overline{FF}$  goes HIGH after the rising edge of Read ( $\overline{R}$ ) during the first read cycle following a full condition (See Figure 6). The FF goes LOW after the falling edge of Write (W) during the write cycle which creates the full condition.

During a Reset cycle, the FF is driven HIGH (inactive).

#### FL/RT

#### First Load/Retransmit (Input; Active LOW)

This is a dual purpose input, dependent upon whether the FIFO is in Single Device Mode or Depth-Expansion Mode.

This pin acts as a FIRST LOAD (FL) pin when in the Depth-Expansion Mode. The device receiving data first will have the FL input tied LOW, while the remaining devices will have the FL pin tied HIGH. The states of the FL and Expansion In  $(\overline{XI})$  pins are used to determine the FIFO's mode of operation, as shown in Tables 1 and 2.

This pin is used as the Retransmit (RT) input during Single Device Mode. The device can be instructed to retransmit the previously written data when RT is pulsed LOW.

#### GND

#### Power Supply, Ground

This pin is the 0 V power supply for the FIFO.

#### NC

#### No Connect

These pins are not connected.

#### Q0-8

#### Data Out (Outputs (9), Three State)

These nine pins are the data outputs for the FIFO. These pins are in a high impedance state whenever Read (R) is HIGH.

#### Read (Input; Active LOW)

The falling edge of Read (R) initiates a read cycle, except when the device is empty, as indicated by the Empty Flag (EF) being LOW. Valid data appears on the outputs (Q0-8) after the falling edge of R. After R goes HIGH, the Data Outputs (Q0-8) will return to a high impedance condition.

#### Reset (Input; Active LOW)

The falling edge of Reset ( $\overline{RS}$ ) is used to reset the FIFO. During Reset, both the read and write pointers are set to the first location in the FIFO. Since the reset cycle initializes the FIFO to an empty condition, the Empty Flag (EF) is driven LOW (active), and both the Half-Full Flag (HF) and Full Flag (FF) are driven HIGH (inactive).

#### **Power Supply**

This pin is the +5 V power supply for the FIFO.

#### Write (Input; Active LOW)

The falling edge of Write (W) initiates a write cycle, except when the device is full, as indicated by the Full Flag  $(\overline{FF})$  being LOW. Data is latched into the FIFO on the rising edge of  $\overline{W}$ .

#### XÏ

#### Expansion In (Input; Active LOW)

Expansion In  $(\overline{XI})$  is grounded to indicate operation in the Single Device or Width-Expansion Modes. In Depth Expansion Mode, the XI pin is connected to the Expansion Out (XO) pin of the previous device, except for the XI pin of the first device which is connected to the XO pin of the last FIFO.

This pin operates at CMOS logic levels, thus providing noise immunity between cascaded devices.

#### XO/HF

#### Expansion Out/Half-Full Flag (Output; Active LOW)

This is a dual purpose output, dependent upon whether the device is in Single Device Mode or Depth Expansion

This pin operates as an Expansion Out  $(\overline{XO})$  signal during Depth Expansion Mode. In this mode, the  $\overline{XO}$  pin is connected to the Expansion Input ( $\overline{XI}$ ) pin of the following device, except for the XO pin of the last device which is connected to the  $\overline{\text{XI}}$  pin of the first device.

When in Single Device Mode (Expansion In  $(\overline{XI})$  pin grounded) this output operates as a Half-Full Flag (HF). After half the FIFO has been filled, the  $\overline{HF}$  will be set LOW at the falling edge of the next Write  $(\overline{W})$  operation. The  $\overline{HF}$  will remain LOW until the difference between the write pointer and read pointer is less than or equal to one half of the total memory of the FIFO. The  $\overline{HF}$  will go

HIGH after the rising edge of  $\overline{R}$  during the read operation which eliminates the half-full condition (See Figure 5).

During a Reset cycle, the HF is driven HIGH (inactive).

This pin operates at CMOS logic levels, thus providing noise immunity between cascaded devices.

#### **FUNCTIONAL DESCRIPTION**

The Am7204A CMOS FIFO is designed around a 4096x9 dual-port static RAM array. (See Figure 1.) RAM-based FIFOs store the data written into them in a sequential pattern.

The dual-port RAM array has dedicated write and read address pointers. The flag logic prevents illogical writes and reads from occurring. The Empty Flag prevents reading while empty, which is a data underflow condition, while the Full Flag prevents writing while full, which is a data overflow condition. Once data that has been stored at a given address is read, it can be overwritten.

Address pointers automatically overflow to address zero after reaching address 4095. Thus the flag status of the FIFO is a function of the difference between the pointers, not their absolute value.

Resetting the FIFO simply initializes both address pointers to address zero. Pulsing Retransmit initializes the read address pointer to zero without affecting the write address pointer.

Expansion Logic is used when implementing a FIFO of a depth greater than that of the Am7204A. The write, read, data-in and data-out lines of the Am7204A are connected in parallel, and the Expansion-Out  $(\overline{XO})$  and the Expansion-I  $(\overline{XI})$  lines are daisy-chained together. The write and read control circuits of the individual FIFOs are automatically enabled and disabled through the handshake between  $\overline{XO}$  and  $\overline{XI}$ .

## **Operational Description**

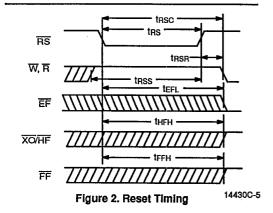

#### Resetting the FIFO

Upon power up, the FIFO must be initialized with a Reset cycle. (See Figure 2.) The states of  $\overline{\text{XI}}$  and  $\overline{\text{FL}}$  are used during the reset cycle to determine the FIFO's mode of operation, as shown in Tables 1 and 2. For a valid reset cycle to occur, both the Read  $(\overline{\text{R}})$  and Write  $(\overline{\text{W}})$  signals must be HIGH tass prior to and tash after the rising edge of Reset  $(\overline{\text{RS}})$ . The reset cycle initializes the FIFO to an empty condition, signified by the Empty Flag  $(\overline{\text{EF}})$  being LOW, active, and both the Half-Full  $(\overline{\text{HF}})$  and Full Flag  $(\overline{\text{FF}})$  being HIGH, inactive.

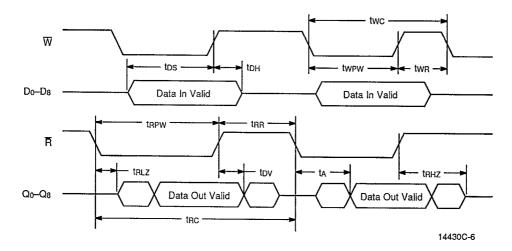

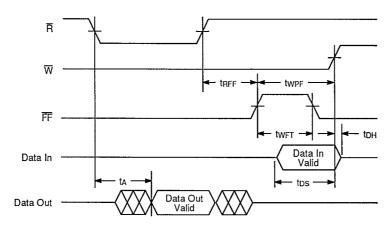

#### Writing Data to the FIFO

The HIGH state of the Full Flag ( $\overline{FF}$ ) indicates that the FIFO is capable of accepting data. The falling edge of Write ( $\overline{W}$ ) initiates a write cycle. (See Figure 3.) Data appearing at inputs Do-Ds tos prior to and toh after the ris ing edge of  $\overline{W}$  will be stored sequentially in the FIFO.

The LOW-to-HIGH transition of the Empty Flag ( $\overline{EF}$ ) occurs twer after the rising edge of  $\overline{W}$  during the first write cycle on an empty FIFO. (See Figure 4.) The Half-Full Flag ( $\overline{HF}$ ) will go LOW tw-F after the falling edge of  $\overline{W}$  during the write operation which creates the half-full condition. (See Figure 5.)  $\overline{HF}$  will remain LOW, while the number of writes to the FIFO exceeds the number of reads by 2049 or more. The Half-Full Flag is not available in Depth-Expansion Mode. The Full Flag ( $\overline{FF}$ ) goes LOW tw-F after the falling edge of  $\overline{W}$  during the write cycle which creates a full condition. (See Figure 6.) A full condition exists when there have been 4096 more write cycles than read cycles. The Full Flag being active prohibits any further write operations, thus preventing data overflow situations.

A special case of write occurs when a write operation is initiated while the part is full. The next read will cause  $\overline{\text{FF}}$  to go inactive, and data can then be latched into the FIFO twpf after the rising edge of  $\overline{\text{FF}}$  (see Figure 9).

#### Reading Data from the FIFO

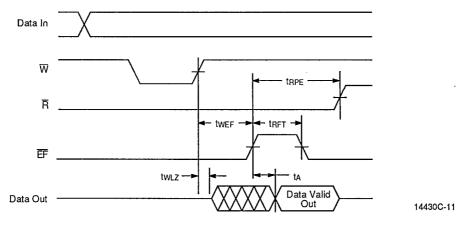

The HIGH state of the Empty Flag ( $\overline{\text{EF}}$ ) indicates that the FIFO is ready to output data. The falling edge of Read ( $\overline{\text{R}}$ ) initiates a read cycle. (See Figure 3.) Valid data appears on the outputs Qo-Q8 ta after the falling edge of  $\overline{\text{R}}$ , and remains until Ibv after the rising edge of  $\overline{\text{R}}$ . Qo-Q8 return to a high-impedance state when  $\overline{\text{R}}$  is inactive, when the FIFO is empty, or when the FIFO is in Depth Expansion Mode but is not active.

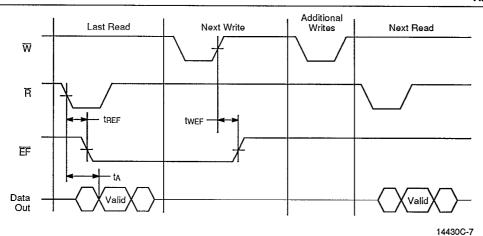

The Full Flag ( $\overline{\text{FF}}$ ) will go HIGH there after the rising edge of  $\overline{\text{R}}$  during the first read cycle following a full condition. (See Figure 6.) The Half-Full Flag ( $\overline{\text{HF}}$ ) will go HIGH therefater the rising edge of  $\overline{\text{R}}$  during the read operation, which eliminates the half-full condition. (See Figure 5). HF will remain HIGH, while the number of writes to the FIFO exceeds the number of reads by 2048 or less. The Half-Full Flag is not available in Depth-Expansion Mode. The HIGH-to-LOW transition of  $\overline{\text{EF}}$  occurs the fater the falling edge of  $\overline{\text{R}}$  during the read cycle, which creates an empty condition. (See Figure 4.) An empty condition exists when there has been an equal number of write cycles and read cycles. The Empty Flag being active prohibits any further read operations, thus preventing a data underflow situation.

A special case of read occurs when a read operation is initiated while the part is empty. The data latched in by the next write will be accessed to ns after the rising edge of  $\overline{\text{EF}}$ . Read is held active, and cannot be deasserted until three after the rising edge of  $\overline{\text{EF}}$  (see Figure 8).

Table 1. Reset and Retransmit Truth Table (Single-Device Configuration/Width-Expansion Mode)

| Mode       |    | Inputs |    | Internal           |                    | Outputs       |               |               |

|------------|----|--------|----|--------------------|--------------------|---------------|---------------|---------------|

| Wode       | RS | FL/RT  | ΧI | Read Pointer       | Write Pointer      | ĒF            | FF            | HF            |

| Reset      | 0  | Х      | 0  | Location zero      | Location zero      | 0             | 1             | 1             |

| Retransmit | 1  | 0      | 0  | Location zero      | Unchanged          | X<br>(Note 1) | X<br>(Note 1) | X<br>(Note 1) |

| Read/Write | 1  | 1      | 0  | Increment (Note 2) | Increment (Note 2) | Х             | Х             | Х             |

#### Notes:

- 1. Flags will change to show correct state according to write pointer.

- 2. Pointers will increment only if corresponding flag is HIGH at the beginning of the cycle.

# Table 2. Reset and First Load Truth Table (Depth-Expansion/Compound-Expansion Mode)

| Mode                    |    | Input         | s              | Interna            | l Status           | Outputs |    |  |

|-------------------------|----|---------------|----------------|--------------------|--------------------|---------|----|--|

| Mode                    | RS | FL/RT         | ΧĪ             | Read Pointer       | Write Pointer      | EF      | FF |  |

| Reset-first device      | 0  | 0             | XO<br>(Note 1) | Location zero      | Location zero      | 0       | 1  |  |

| Reset all other devices | 0  | 1             | XO<br>(Note 1) | Location zero      | Location zero      | 0       | 1  |  |

| Read/Write              | 1  | X<br>(Note 2) | XO<br>(Note 1) | Increment (Note 3) | Increment (Note 3) | X       | ×  |  |

- 1.  $\overline{XI}$  is connected to  $\overline{XO}$  of previous device. See Figure 12.

- 2. Same as during Reset Cycle.

- 3. Pointers will increment only if corresponding flag is HIGH at the beginning of the cycle.

Figure 3. Asynchronous Write and Read Timing

Figure 4. Empty Flag Timing

Note:

Depending on the precise phase of  $\overline{W}$  and  $\overline{R}$ , the Half-Full Flag may appear as a pulse of arbitrarily short duration of either polarity when  $\overline{W}$  and  $\overline{R}$  are operating asynchronously near half full.

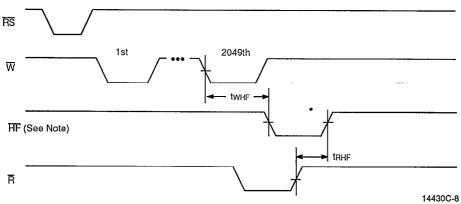

Figure 5. Half-Full Flag Timing

#### Half-Full Flag

The Half-Full ( $\overline{HF}$ ) Flag will be active LOW only when the net balance of the words written into the FIFO exceeds the number of words read out by 2049 or more. (See Figure 5.)

Care should be exercised in using the Half-Full Flag, because it is capable of producing arbitrarily short pulses. For example, if the FIFO contains 2049 words, and Read and Write pulses are applied simultaneously, the HF flag may produce an arbitrarily short pulse, depending on the precise phase of Read and Write.

$\overline{\text{HF}}$  will always settle to the correct state after the appropriate delay,  $t_{\text{WHF}}$  or  $t_{\text{RHF}}$ . This property of the Half-Full Flag is clearly a function of the dynamic relation between  $\overline{W}$  and  $\overline{R}$ . Generally, the use of level-sensitive, rather than edge-sensitive, status detection circuits will alleviate this hazard.

#### Retransmit

The retransmit function resets the read address pointer allowing the data that was previously read to be read again. This capability is useful when the block of data being transferred through the FIFO doesn't exceed the FIFO's depth and is intended for use when there are 4096 or less writes between reset cycles.

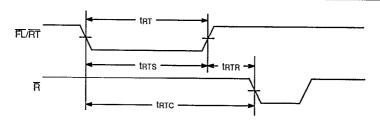

The  $\overline{FL/RT}$  is used as the Retransmit ( $\overline{RT}$ ) input in Single-Device Mode. The retransmit capability is intended for use when there are 4096 or less writes between reset cycles.  $\overline{RT}$ , an active LOW-going pulse of at least tat in duration, initializes the internal read pointer to address zero and leaves the write pointer unaffected.  $\overline{R}$  must be HIGH during the retransmit cycle. The first read cycle should not start until tata after the rising edge of  $\overline{RT}$ . The flags may change state during this cycle, but they will accurately reflect the new state of the FIFO tata after the falling edge of  $\overline{RT}$ . (See Figure 7 and Table 1).

#### Single-Device/Width-Expansion Modes

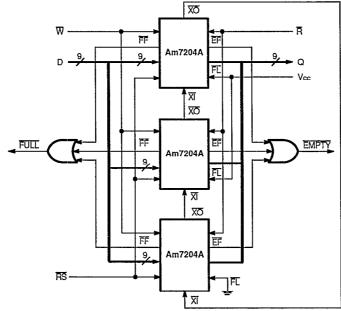

Single-Device and Width-Expansion Modes are configured by grounding the Expansion-In  $(\overline{XI})$  input. (See Figures 12 and 13, and Table 1.) During these modes of operation, the Half-Full Flag and Retransmit features are available. The Am7204A can be expanded in width to create FIFOs of word widths greater than nine bits. In

Width-Expansion Mode all of the control line inputs are common to all devices. (See Figure 13.) Creating composite status flags can pose two hazards. 1) OR-ing the flag outputs is fine for the HIGH-to-LOW transition, because the skew between devices is masked out. However, when the flags make a LOW-to-HIGH transition, a false composite flag is generated due to the skew between devices. 2) The converse is true when the flags are AND-ed: the LOW-to-HIGH transition is fine, and the HIGH-to-LOW generates a false flag. These two hazards can be avoided if one device's flags are used as the flags for the expanded FIFO, and the write control circuitry and read control circuitry is designed to hold off sampling the flags until the worst case settling time (tweeperson).

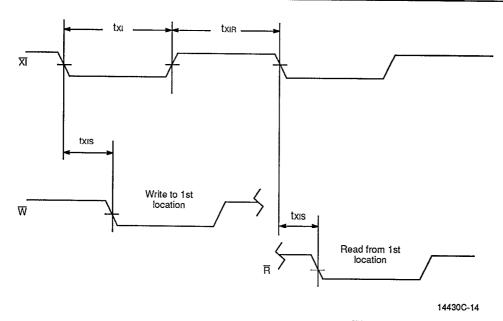

#### Depth-Expansion Mode

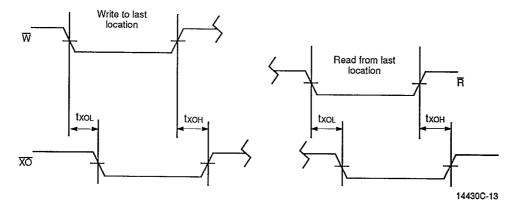

Depth-Expansion Mode is configured during the Reset cycle. (See Figure 14 and Table 2.) Expansion Out  $(\overline{XO})$  of one device must be connected to Expansion In  $(\overline{XI})$  of the next device, with  $\overline{XO}$  of the last device being connected to  $\overline{XI}$  of the first device. The device that is to receive data first has its First Load  $(\overline{FL})$  input tied LOW, while all other devices must have this input HIGH. Write and read control is passed between devices using  $\overline{XO}$  and  $\overline{XI}$ . A LOW-going pulse on  $\overline{XO}$  occurs when the last physical location of an active device, address 4096, is written to, and another LOW-going pulse occurs when the last physical location of an active device is read. Only one device is enabled for writes, and only one device is enabled for reads at any given time.

When expanding in depth, a composite Full Flag must be created by OR-ing all the FF outputs together. Likewise, a composite Empty Flag is created by OR-ing all the EF outputs together. The Half-Full Flag and Retransmit functions are not available in Depth-Expansion Mode.

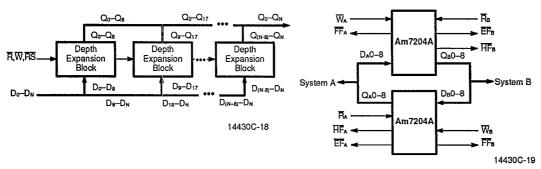

#### Compound Expansion

FIFOs of greater width and depth than the Am7204A can be created by using both Width-Expansion Mode and Depth-Expansion Mode simultaneously. (See Figure 15.)

14430C-10

Note:

EF, HF and FF may change state during Retransmit as a result of the offset of the read and write pointers, but the flags will be valid at the three transmits are resulted to the read and write pointers.

Figure 7. Retransmit Timing

Note: (tRPE = tRPW, tRFT = tREF)

Figure 8. Read Data Flow-Through Mode

Note: (twpF = twpw, twfT = twFF)

14430C-12

Figure 9. Write Data Flow-Through Mode

Figure 10.  $\overline{\text{XO}}$  Delay from Clock

Figure 11. 1st Clock Pulse Delay from  $\overline{XI}$

14430C-16

Figure 12. Single FIFO Configuration

Figure 13. Width-Expansion to Form a 4096 x 18 FIFO

Figure 14. Depth-Expansion to Form 12,288x9 FIFO

Figure 15. FIFO Array Using Both Width-Expansion and Depth-Expansion Techniques

Figure 16. Bidirectional FIFO Configuration

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage, Vcc

-0.5 V to +7.0 V

Input Voltage

-0.5 V to Vcc +0.5 V

Ambient Temperature with Power Applied

-55°C to +125°C

Storage Temperature

-55°C to +150°C

Power Dissipation

1.0 W

DC Output Current

50 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

#### Commercial (C) Devices

Ambient Temperature (T<sub>A</sub>) . . . . . 0°C to 70°C Supply Voltage, (Vcc) . . . . . . . +4.5 V to +5.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over COMMERCIAL operating range unless otherwise specified

|                  |                                                                                                                             |      |       | I    |       |      |       | i    | 04 <b>A</b> -50 |      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|------|-------|------|-----------------|------|

| Parameter        |                                                                                                                             |      | 15 ns |      | 25 ns |      | 35 ns |      | 50 ns           |      |

| Symbol           | Parameter Description                                                                                                       | Min. | Max.  | Min. | Max.  | Min. | Max.  | Min. | Max.            | Unit |

| ΙιL              | Input Leakage Current (any input) (Note 1)                                                                                  | -1   | 1     | -1   | 1     | -1   | 1     | -1   | 1               | μА   |

| Ιιο              | Output Leakage Current (data outputs) (Note 2)                                                                              | -10  | 10    | -10  | 10    | -10  | 10    | -10  | 10              | μА   |

| ViH              | Input High Voltage (all inputs except $\overline{X!}$ ) (Note 3)                                                            | 2.0  |       | 2.0  |       | 2.0  |       | 2.0  |                 | ٧    |

| VIL              | Input Low Voltage (all inputs except XI)<br>(Note 3)                                                                        |      | 8.0   |      | 0.8   |      | 0.8   |      | 0.8             | ٧    |

| Vihxi            | Input High Voltage, XI (Note 3)                                                                                             | 3.5  |       | 3.5  |       | 3.5  |       | 3.5  |                 | V    |

| Vilxi            | Input Low Voltage, XI (Note 3)                                                                                              |      | 1.5   |      | 1.5   |      | 1.5   |      | 1.5             | V    |

| Vон              | Output Logic "1" Voltage loн = -2 mA                                                                                        | 2.4  |       | 2.4  |       | 2.4  |       | 2.4  |                 | V    |

| Vol              | Output Logic "0" Voltage loL = 8 mA                                                                                         |      | 0.4   |      | 0.4   |      | 0.4   |      | 0.4             | V    |

| Icc <sub>1</sub> | Average Vcc Power Supply Current (Note 4)                                                                                   |      | 90    |      | 70    |      | 60    |      | 60              | mA   |

| lcc2             | Average Standby Current $(\overline{R} = \overline{W} = \overline{RS} = \overline{FL/RT} = 2.4 \text{ V}) \text{ (Note 4)}$ |      | 15    |      | 15    |      | 15    |      | 15              | mA   |

| lcc3             | Power Down Current<br>(all inputs = Vcc - 0.2 V) (Note 4)                                                                   |      | 2     |      | 2     |      | 2     |      | 2               | mA   |

- 1. Measurements with GND ≤ V<sub>IN</sub> ≤ V<sub>CC</sub>.

- 2.  $\overline{R} \ge V_{IH}$ , GND  $\le V_{OUT} \le V_{CC}$ .

- 3. VIL and VIH are input conditions of output tests and are not themselves directly tested. VIL and VIH are absolute voltages with respect to device ground and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

- 4. Icc measurements are made with outputs open.

# SWITCHING CHARACTERISTICS over COMMERCIAL operating range unless otherwise specified

| Specified<br>Parameter |                                                |         | Am72 | 04 <b>A</b> -15 | Am72 | 04A-25   | Am72 | 04A-35 | Am72 | 04 <b>A-</b> 50 |      |

|------------------------|------------------------------------------------|---------|------|-----------------|------|----------|------|--------|------|-----------------|------|

| Symbol                 | Parameter Description                          | Figures | Min. |                 |      |          |      |        |      | Max.            | Unit |

| Write and F            | lag Timing                                     |         |      |                 |      |          |      |        |      |                 |      |

| twc                    | Write Cycle Time                               | 3       | 25   |                 | 35   |          | 45   |        | 65   |                 | ns   |

| twpw                   | Write Pulse Width                              | 3       | 15   |                 | 25   |          | 35   |        | 50   |                 | ns   |

| twr                    | Write Recovery Time                            | 3       | 10   |                 | 10   |          | 10   |        | 15   |                 | ns   |

| tos                    | Data Setup Time                                | 3,9     | 12   |                 | 15   |          | 18   |        | 30   |                 | ns   |

| tон                    | Data Hold Time                                 | 3,9     | 0    |                 | 0    |          | 0    |        | 5    |                 | ns   |

| twff                   | Write LOW to Full Flag LOW                     | 6,9     |      | 24              |      | 25       |      | 30     |      | 45              | ns   |

| twhe                   | Write LOW to Half-Full Flag LOW                | 5       |      | 30              |      | 35       |      | 45     |      | 65              | ns   |

| twer                   | Write HIGH to Empty Flag HIGH                  | 4,8     |      | 24              |      | 25       |      | 30     |      | 45              | ns   |

| twLz                   | Write Pulse HIGH to Data Bus at LOW Z (Note 1) | 8       | 5    |                 | 5    |          | 10   |        | 10   |                 | ns   |

| twpF                   | Write Pulse Width after FF HIGH                | ø       | 15   |                 | 25   |          | 35   |        | 50   |                 | ns   |

| Read and F             | lag Timing                                     |         | ·    |                 |      |          |      |        |      |                 |      |

| trc                    | Read Cycle Time                                | 3       | 25   |                 | 35   |          | 45   |        | 65   |                 | ns   |

| ta                     | Access Time                                    | 3,4,8,9 |      | 15              |      | 25       |      | 35     |      | 50              | ns   |

| trr                    | Read Recovery Time                             | 3       | 10   |                 | 10   |          | 10   |        | 15   |                 | ns   |

| trpw                   | Read Pulse Width                               | 3       | 15   |                 | 25   |          | 35   |        | 50   |                 | ns   |

| truz                   | Read Pulse LOW to Data Bus at LOW Z (Note 1)   | 3       | 5    |                 | 5    |          | 5    |        | 5    |                 | ns   |

| tov                    | Data Valid from Read Pulse HIGH                | 3       | 5    |                 | 5    |          | 5    |        | 5    | <u> </u>        | ns   |

| trHz                   | Read Pulse HIGH to Data Bus at HIGH Z (Note 1) | 3       |      | 15              |      | 18       |      | 20     |      | 30              | ns   |

| trff                   | Read HIGH to Full Flag HIGH                    | 6,9     |      | 24              |      | 25       |      | 30     | ļ    | 45              | ns   |

| trhf                   | Read HIGH to Half-Full Flag HIGH               | 5       |      | 30              |      | 35       |      | 45     |      | 65              | ns   |

| tref                   | Read LOW to Empty Flag LOW                     | 4,8     |      | 24              |      | 25       |      | 30     |      | 45              | ns   |

| TRPE                   | Read Pulse Width after EF HIGH                 | 8       | 15   |                 | 25   |          | 35   |        | 50   |                 | ns   |

| Reset Timi             | ng                                             |         |      |                 |      |          |      |        |      |                 |      |

| trsc                   | Reset Cycle Time                               | 2       | 25   |                 | 35   |          | 45   |        | 65   | Ī               | ns   |

| trs                    | Reset Pulse Width                              | 2       | 15   |                 | 25   |          | 35   |        | 50   |                 | ns   |

| trss                   | Reset Setup Time                               | 2       | 15   |                 | 25   |          | 35   |        | 50   | <u> </u>        | ns   |

| trsr                   | Reset Recovery Time                            | 2       | 10   |                 | 10   | <u> </u> | 10   |        | 15   | L               | ns   |

| tefl                   | Reset to Empty Flag LOW                        | 2       |      | 25              |      | 35       |      | 45     |      | 65              | ns   |

| theh                   | Reset to Half-Full Flag High                   | 2       |      | 25              |      | 35       |      | 45     |      | 65              | ns   |

| tғғн                   | Reset to Full Flag HIGH                        | 2       |      | 25              |      | 35       |      | 45     |      | 65              | ns   |

| Retransmi              | Timing                                         |         |      |                 |      |          |      |        |      |                 |      |

| trrc                   | Retransmit Cycle Time                          | 7       | 45   |                 | 45   |          | 45   |        | 65   |                 | ns   |

| ter                    | Retransmit Pulse Width                         | 7       | 35   |                 | 35   |          | 35   |        | 50   |                 | ns   |

| trts                   | Retransmit Setup Time (Note 2)                 | 7       | 15   |                 | 25   |          | 35   |        | 50   |                 | ns   |

| trtr                   | Retransmit Recovery Time                       | 7       | 10   |                 | 10   |          | 10   |        | 15   |                 | ns   |

#### Notes:

Am7204A 2-89

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where these parameters may be affected.

<sup>2.</sup> Values are guaranteed by design and are not currently tested.

## SWITCHING CHARACTERISTICS (continued)

| Parameter |                           |         | Am7204A-15 |      | Am7204A-25 |      | Am7204A-35 |      | Am72 | 04A-50 | [    |

|-----------|---------------------------|---------|------------|------|------------|------|------------|------|------|--------|------|

| Symbol    | Parameter Description     | Figures | Min.       | Max. | Min.       | Max. | Min.       | Max. | Min. | Max.   | Unit |

| Expansion | Timing                    |         |            |      |            |      |            |      |      |        |      |

| txol      | Read/Write to XO LOW      | . 10    |            | 25   |            | 25   |            | 35   |      | 50     | ns   |

| tхон      | Read/Write to XO HIGH     | 10      |            | 25   |            | 25   |            | 35   |      | 50     | ns   |

| txı       | XI Pulse Width (Note 2)   | 11      | 15         |      | 25         |      | 35         |      | 50   |        | ns   |

| txir      | XI Recovery Time (Note 2) | 11      | 10         |      | 10         |      | 10         |      | 10   |        | ns   |

| txis      | XI Setup Time             | 11      | 10         |      | 10         |      | 10         |      | 10   |        | ns   |

- These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where these parameters may be affected.

- 2. Values are guaranteed by design and are not currently tested.

# ABSOLUTE MAXIMUM RATINGS Supply Voltage, Vcc -0.5 V to +7.0 V Input Voltage -0.5 V to Vcc +0.5 V Ambient Temperature with Power Applied -55°C to +125°C Storage Temperature -65°C to +155°C Power Dissipation 1.0 W DC Output Current 50 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

#### Miltary (M) Devices\*

Case Temperature (Tc) . . . . . -55°C to 125°C Supply Voltage, (Vcc) . . . . . . . . +4.5 V to +5.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

\*Military product is manufactured in compliance with the latest revision of MIL-STD-883, Class B.

#### DC CHARACTERISTICS over MILITARY operating range unless otherwise specified.

| Parameter | . '                                                             | Am7204A-30<br>t <sub>A</sub> = 30 ns |      | Am72 |      |      |

|-----------|-----------------------------------------------------------------|--------------------------------------|------|------|------|------|

| Symbol    | Parameter Description                                           | Min.                                 | Max. | Min. | Max. | Unit |

| lı.       | Input Leakage Current (any input) (Note 1)                      | 10                                   | 10   | -10  | 10   | μΑ   |

| lio       | Output Leakage Current (data outputs)<br>(Note 2)               | -10                                  | 10   | -10  | 10   | μА   |

| ViH       | Input High Voltage (all inputs except XI) (Note 3)              | 2.2                                  |      | 2.2  |      | V    |

| VıL       | Input Low Voltage (all inputs except $\overline{XI}$ ) (Note 3) |                                      | 0.8  |      | 0.8  | V    |

| Vihxi     | Input High Voltage, XI (Note 3)                                 | 3.5                                  |      | 3.5  |      | V    |

| VILXI     | Input Low Voltage, XI (Note 3)                                  |                                      | 1.5  |      | 1.5  | V    |

| Vон       | Output Logic "1" Voltage Ioн = -2 mA                            | 2.4                                  |      | 2.4  |      | V    |

| Vol       | Output Logic "0" Voltage loL = 8 mA                             |                                      | 0.4  |      | 0.4  | V    |

| lcc1      | Average Vcc Power Supply Current (Note 4)                       |                                      | 100  |      | 90   | mA   |

| lcc2      | Average Standby Current<br>(R = W = RS = FL/RT = ViH) (Note 4)  |                                      | 15   |      | 15   | mA   |

| lcc3      | Power Down Current (all inputs = Vcc -0.2 V) (Note 4)           |                                      | 4    |      | 4    | mA   |

- 1. Measurements with GND ≤ V<sub>IN</sub> ≤ V<sub>CC</sub>.

- 2. R ≥ ViH, GND ≤ Vout ≤ Vcc.

- 3. VIL and VIH are input conditions of output tests and are not themselves directly tested. VIL and VIH are absolute voltages with respect to device ground and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

- 4. Icc measurements are made with outputs open.

# SWITCHING CHARACTERISTICS over MILITARY operating range unless otherwise specified

| Parameter    |                                                |         | Am720 | 4A-30 | Am720 | 04A-50 |     |

|--------------|------------------------------------------------|---------|-------|-------|-------|--------|-----|

| Symbol       | Parameter Description                          | Figures | Min.  | Max.  | Min.  | Max.   | Uni |

| Write and F  |                                                |         |       |       |       |        |     |

| two          | Write Cycle Time                               | 3       | 40    |       | 65    |        | ns  |

| twpw         | Write Pulse Width                              | 3       | 30    |       | 50    |        | ns  |

| twa          | Write Recovery Time                            | 3       | 10    |       | 15    |        | ns  |

| tos          | Data Setup Time                                | 3,9     | 18    |       | 30    |        | ns  |

| ton          | Data Hold Time                                 | 3,9     | 0     |       | 5     |        | ns  |

| twff         | Write LOW to Full Flag LOW                     | 6,9     |       | 30    |       | 45     | ns  |

| twhF         | Write LOW to Half-Full Flag LOW                | 5       | ····· | 40    |       | 65     | ns  |

| twer         | Write HIGH to Empty Flag HIGH                  | 4,8     |       | 30    |       | 45     | ns  |

| twLz         | Write Pulse HIGH to Data Bus at LOW Z (Note 1) | 8       | 5     |       | 10    |        | ns  |

| twpf         | Write Pulse Width after FF HIGH                | 9       | 30    |       | 50    |        | ns  |

| Read and Fl  | ag Timing                                      |         | '     | ا     | ****  |        |     |

| trc          | Read Cycle Time                                | 3       | 40    |       | 65    |        | ns  |

| ta           | Access Time                                    | 3,4,8,9 |       | 30    |       | 50     | ns  |

| trr          | Read Recovery Time                             | 3       | 10    |       | 15    |        | ns  |

| trpw         | Read Pulse Width                               | 3       | 30    |       | 50    |        | ns  |

| trl <i>z</i> | Read Pulse LOW to Data Bus at LOW Z (Note 1)   | 3       | 5     |       | 5     |        | ns  |

| tov          | Data Valid from Read Pulse HIGH                | 3       | 5     |       | 5     |        | ns  |

| trhz         | Read Pulse HIGH to Data Bus at HIGH Z (Note 1) | 3       |       | 20    |       | 30     | ns  |

| tree         | Read HIGH to Full Flag HIGH                    | 6,9     |       | 30    |       | 45     | ns  |

| trhf         | Read HIGH to Half-Full Flag HIGH               | 5       |       | 40    |       | 65     | ns  |

| tref         | Read LOW to Empty Flag LOW                     | 4,8     |       | 30    |       | 45     | ns  |

| trpe         | Read Pulse Width after EF HIGH                 | 8       | 30    |       | 50    |        | ns  |

| Reset Timing | g                                              |         | ,     |       |       |        |     |

| trsc         | Reset Cycle Time                               | 2       | 40    |       | 65    |        | ns  |

| trs          | Reset Pulse Width                              | 2       | 30    |       | 50    |        | ns  |

| trss         | Reset Setup Time                               | 2       | 30    |       | 50    |        | ns  |

| trsr         | Reset Recovery Time                            | 2       | 10    |       | 15    |        | ns  |

| tefl         | Reset to Empty Flag LOW                        | 2       |       | 40    |       | 65     | ns  |

| theh         | Reset to Half-Full Flag High                   | 2       |       | 40    |       | 65     | ns  |

| tffH         | Reset to Full Flag HIGH                        | 2       |       | 40    |       | 65     | ns  |

| Retransmit T | liming                                         |         | 1     |       |       | 00     | 113 |

| trrc         | Retransmit Cycle Time                          | 7       | 40    |       | 65    |        | ns  |

| trt          | Retransmit Pulse Width                         | 7       | 30    |       | 50    |        | ns  |

| ters         | Retransmit Setup Time (Note 2)                 | 7       | 30    |       | 50    |        |     |

| trtr         | Retransmit Recovery Time                       | 7       | 10    |       | 15    |        | ns  |

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where these parameters may be affected.

<sup>2.</sup> Values are guaranteed by design and are not currently tested.

## **SWITCHING CHARACTERISTICS (continued)**

| Parameter |                           |         | Am720 | Am7204A-30 |      | Am7204A-50 |      |

|-----------|---------------------------|---------|-------|------------|------|------------|------|

| Symbol    | Parameter Description     | Figures | Min.  | Max.       | Min. | Max.       | Unit |

| Expansion | Timing                    |         |       |            |      |            |      |

| txol.     | Read/Write to XO LOW      | 10      |       | 30         |      | 50         | ns   |

| tхон      | Read/Write to XO HIGH     | 10      |       | 30         |      | 50         | ns   |

| txı       | XI Pulse Width (Note 2)   | 11      | 30    |            | 50   |            | ns   |

| txin      | XI Recovery Time (Note 2) | 11      | 10    |            | 10   |            | ns   |

| txis      | XI Setup Time             | 11      | 15    |            | 15   |            | ns   |

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where these parameters may be affected.

<sup>2.</sup> Values are guaranteed by design and are not currently tested.

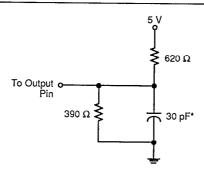

## **AC TEST CONDITIONS**

| Input pulse levels             | GND to 3.0 V  |

|--------------------------------|---------------|

| Input rise and fall times      | 5 ns          |

| Input timing reference levels  | 1.5 V         |

| Output timing reference levels | 1.5 V         |

| Output load                    | See Figure 17 |

14430C-20

Figure 17. AC Test Load

| Parameter<br>Symbol | Parameter Description (Note1) | Test Conditions | Тур. | Unit |

|---------------------|-------------------------------|-----------------|------|------|

| CIN                 | Input capacitance             | VIN = 0 V       | 5    | pF   |

| Cout                | Output capacitance            | Vout = 0 V      | 7    | ρF   |

#### Note:

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

<sup>\*</sup> Includes jig and scope capacitances.