# Am2901B/Am2901C

Four-Bit Bipolar Microprocessor Slice

#### DISTINCTIVE CHARACTERISTICS

- Two-address architecture –

Independent simultaneous access to two working registers saves machine cycles.

- Eight-function ALU Performs addition, two subtraction operations, and five logic functions on two source operands.

- Expandable –

Connect any number of Am2901s together for longer word lengths.

- Left/right shift independent of ALU Add and shift operations take only one cycle.

- Four status flags –

Carry, overflow, zero, and negative.

- Flexible data source selection ALU data is selected from five source ports for a total of

203 source operand pairs for every ALU function.

#### **GENERAL DESCRIPTION**

The Am2901 industry standard four-bit microprocessor slice is a high-speed cascadable ALU intended for use in CPUs, peripheral controllers, and programmable microprocessors. The microinstruction flexibility of the Am2901 permits efficient emulation of almost any digital computing machine.

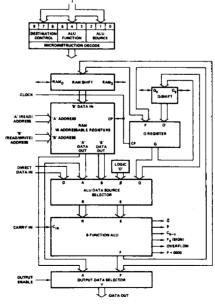

The device, as shown in the block diagram below, consists of a 16-word by 4-bit two-port RAM, a high-speed ALU, and the associated shifting, decoding and multiplexing circuitry. The nine-bit microinstruction word is organized into three

groups of three bits each and selects the ALU source operands, the ALU function, and the ALU destination register. The microprocessor is cascadable with full look ahead or with ripple carry, has three-state outputs, and provides various status flag outputs from the ALU. AMD's ion-implanted micro-oxide (IMOX) processing is used to fabricate the 40-lead LSI chip.

The Am2901C is a plug-in replacement for the Am2901B, but is 33% faster than the Am2901B.

#### MICROPROCESSOR SLICE BLOCK DIAGRAM

BD002120

### RELATED PRODUCTS

| Part No. | Description                            |

|----------|----------------------------------------|

| Am2902   | Carry Look-Ahead Generator             |

| Am2904   | Status and Shift Control Unit          |

| Am2910   | Microprogram Controller                |

| Am2914   | Vectored Priority Interrupt Controller |

| Am2917   | Bus Transceiver                        |

| Am2918   | Pipeline Register                      |

| Am2920   | Octal Register                         |

| Am2922   | Condition Code MUX                     |

| Am2925   | System Clock Generator                 |

| Am2940   | DMA Address Generator                  |

| Am2952   | Bidirectional I/O Port                 |

| Am27S35  | Registered PROM                        |

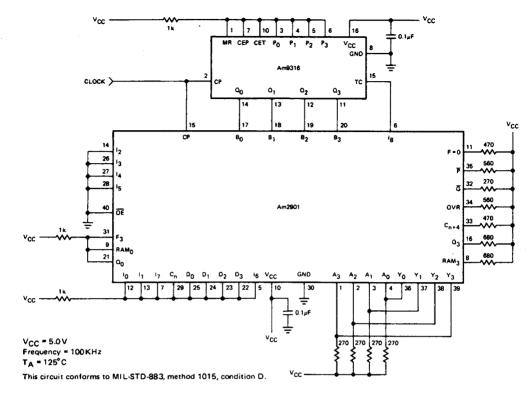

For applications information see Chapters III and IV of Bit Slice Microprocessor Design, by Mick and Brick, McGraw Hill Publishers.

#

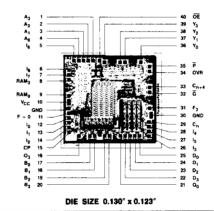

Note: Pin 1 is marked for orientation Figure 1.

#### METALLIZATION AND PAD LAYOUT

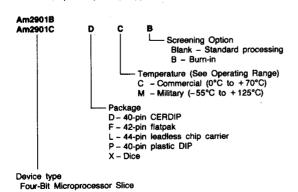

#### ORDERING INFORMATION

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

| Valid Combinations |                                                |  |  |  |  |  |

|--------------------|------------------------------------------------|--|--|--|--|--|

| Am2901B            | PC<br>DC, DCB, DMB<br>FMB<br>XC, XM            |  |  |  |  |  |

| Am2901C            | PC<br>DC, DCB, DMB<br>FMB<br>LC, LMB<br>XC, XM |  |  |  |  |  |

#### **Valid Combinations**

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

#### PIN DESCRIPTION

| Pin No.          | Name                               | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 3, 2, 1       | A <sub>0-3</sub>                   | 1   | The four address inputs to the register stack used to select one register whose contents are displayed through the A-<br>port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17, 18<br>19, 20 | B <sub>0-3</sub>                   | 1   | The four address inputs to the register stack used to select one register whose contents are displayed through the B-port and into which new data can be written when the clock goes LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  | 10-8                               | 1   | The nine instruction control lines. Used to determine what data sources will be applied to the ALU (I012), what function the ALU will perform (I345), and what data is to be deposited in the Q-register or the register stack (I678).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16               | Q <sub>3</sub><br>RAM <sub>3</sub> | 1/0 | A shift line at the MSB of the Q register (Q <sub>3</sub> ) and the register stack (RAM <sub>3</sub> ). Electrically these lines are three-state outputs connected to TTL inputs internal to the device. When the destination code on I <sub>678</sub> indicates an up shift (octal 6 or 7) the three-state outputs are enabled and the MSB of the Q register is available on the Q <sub>3</sub> pin and the MSB of the ALU output is available on the RAM <sub>3</sub> pin. Otherwise, the three-state outputs are electrically QFF (high-impedance) and the pins are electrically LS-TTL inputs. When the destination code calls for a down shift, the pins are used as the data inputs to the MSB of the Q register (octal 4) and RAM (octal 4 or 5). |

| 21, 9            | Q <sub>0</sub><br>RAM <sub>0</sub> | 1/0 | Shift lines like Q <sub>3</sub> and RAM <sub>3</sub> , but at the LSB of the Q-register and RAM. These pins are tied to the Q <sub>3</sub> and RAM <sub>3</sub> pins of the adjacent device to transfer data between devices for up and down shifts of the Q register and ALU data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 25, 24<br>23, 22 | D <sub>0-3</sub>                   | 1   | Direct data inputs. A four-bit data field which may be selected as one of the ALU data sources for entering data into the device. D <sub>0</sub> is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

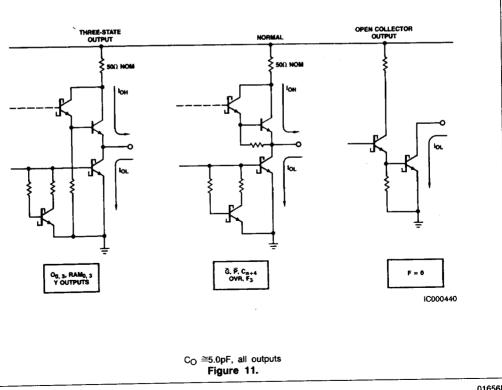

| 36, 37<br>38, 39 | Y <sub>0-3</sub>                   | 0   | The four data outputs. These are three-state output lines. When enabled, they display either the four outputs of the ALU or the data on the A-port of the register stack, as determined by the destination code 1678.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 40               | ŌĒ                                 | 1   | Output Enable. When OE is HIGH, the Y outputs are OFF; when OE is LOW, the Y outputs are active (HIGH or LOW).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 32, 35           | G, P                               | 0   | The carry generate and propagate outputs of the internal ALU. These signals are used with the Am2902 for carry-lookahead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 34               | OVR                                | 0   | Overflow. This pin is logically the Exclusive-OR of the carry-in and carry-out of the MSB of the ALU. At the most significant end of the word, this pin indicates that the result of an arithmetic two's complement operation has overflowed into the sign-bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11               | F = 0                              | 0   | This is an open collector output which goes HIGH (OFF) if the data on the four ALU outputs F <sub>0-3</sub> are all LOW. In positive logic, it indicates the result of an ALU operation is zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 31               | F <sub>3</sub>                     | 10  | The most significant ALU output bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 29               | C <sub>n</sub>                     | 1   | The carry-in to the internal ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 33               | Cn + 4                             | 0   | The carry-out of the internal ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15               | СР                                 | ì   | The clock input. The Q register and register stack outputs change on the clock LOW-to-HIGH transition. The clock LOW time is internally the write enable to the 16 x 4 RAM which compromises the "master" latches of the register stack. While the clock is LOW, the "slave" latches on the RAM outputs are closed, storing the data previously on the RAM outputs. This allows synchronous master-slave operation of the register stack.                                                                                                                                                                                                                                                                                                                |

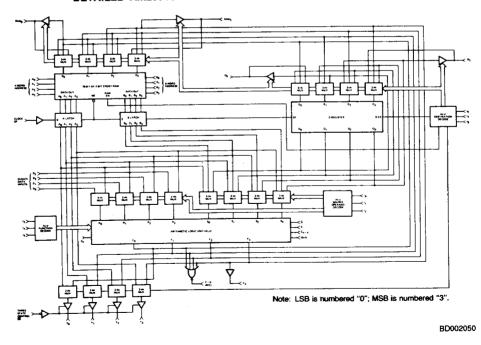

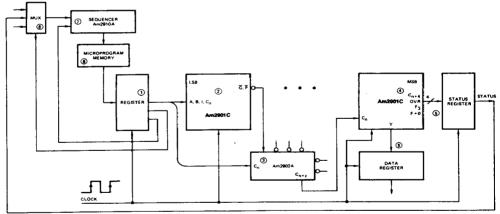

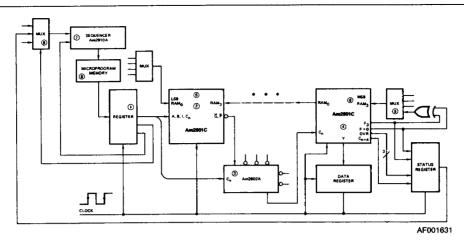

## DETAILED Am2901C MICROPROCESSOR BLOCK DIAGRAM

#### **ARCHITECTURE**

A detailed block diagram of the bipolar microprogrammable microprocessor structure is shown in Figure 1. The circuit is a four-bit slice cascadable to any number of bits. Therefore, all data paths within the circuit are four bits wide. The two key elements in the Figure 1 block diagram are the 16-word by 4-bit 2-port RAM and the high-speed ALU.

Data in any of the 16 words of the Random Access Memory (RAM) can be read from the A-port of the RAM as controlled by the 4-bit A address field input. Likewise, data in any of the 16 words of the RAM as defined by the B address field input can be simultaneously read from the B-port of the RAM. The same code can be applied to the A select field and B select field in which case the identical file data will appear at both the RAM A-port and B-port outputs simultaneously.

When enabled by the RAM write enable (RAM EN), new data is always written into the file (word) defined by the B address field of the RAM. The RAM data input field is driven by a 3-input multiplexer. This configuration is used to shift the ALU output data (F) if desired. This three-input multiplexer scheme allows the data to be shifted up one bit position, shifted down one bit position, or not shifted in either direction.

The RAM A-port data outputs and RAM B-port data outputs drive separate 4-bit latches. These latches hold the RAM data while the clock input is LOW. This eliminates any possible race conditions that could occur while new data is being written into the RAM.

The high-speed Arithmetic Logic Unit (ALU) can perform three binary arithmetic and five logic operations on the two 4-bit input words R and S. The R input field is driven from a 2-input multiplexer, while the S input field is driven from a 3-input multiplexer. Both multiplexers also have an inhibit capability; that is, no data is passed. This is equivalent to a "zero" source operand.

Referring to Figure 2, the ALU R-input multiplexer has the RAM A-port and the direct data inputs (D) connected as inputs. Likewise, the ALU S-input multiplexer has the RAM A-port, the RAM B-port and the Q register connected as inputs.

This multiplexer scheme gives the capability of selecting various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. These five inputs, when taken two at a time, result in ten possible combinations of source operand pairs. These combinations include AB, AD, AQ, AO, BD, BQ, BO, DQ, D0 and Q0. It is apparent that AD, AQ and A0 are somewhat redundant with BD, BQ and B0 in that if the A address and B address are the same, the identical function results. Thus, there are only seven completely non-redundant source operand pairs for the ALU. The Am2901 microprocessor implements eight of these pairs. The microinstruction inputs used to select the ALU source operands are the I<sub>Q</sub>, I<sub>1</sub>, and I<sub>2</sub> inputs. The definition of I<sub>Q</sub>, I<sub>1</sub>, and I<sub>2</sub> for the eight source operand combinations are as shown in Figure 3. Also shown is the octal code for each selection.

The two source operands not fully described as yet are the D input and Q input. The D input is the four-bit wide direct data field input. This port is used to insert all data into the working registers inside the device. Likewise, this input can be used in the ALU to modify any of the internal data files. The Q register is a separate 4-bit file intended primarily for multiplication and division routines but it can also be used as an accumulator or holding register for some applications.

The ALU itself is a high-speed arithmetic/logic operator capable of performing three binary arithmetic and five logic functions. The I<sub>3</sub>, I<sub>4</sub>, and I<sub>5</sub> microinstruction inputs are used to select the ALU function. The definition of these inputs is

shown in Figure 4. The octal code is also shown for reference. The normal technique for cascading the ALU of several devices is in a look-ahead carry mode. Carry generate,  $\overline{G}$ , and carry propagate,  $\overline{P}$ , are outputs of the device for use with a carry-look-ahead-generator such as the Am2902. A carry-out,  $C_{n+4}$ , is also generated and is available as an output for use as the carry flag in a status register. Both carry-in  $(C_n)$  and carry-out  $(C_{n+4})$  are active HIGH.

The ALU has three other status-oriented outputs. These are  $F_3$ , F=0, and overflow (OVR). The  $F_3$  output is the most significant (sign) bit of the ALU and can be used to determine positive or negative results without enabling the three-state data outputs.  $F_3$  is non-inverted with respect to the sign bit output  $Y_3$ . The F=0 output is used for zero detect. It is an open-collector output and can be wire OR'ed between microprocessor slices. F=0 is HIGH when all F outputs are LOW. The overflow output (OVR) is used to flag arithmetic operations that exceed the available two's complement number range. The overflow output (OVR) is HIGH when overflow exists. That is, when  $C_{n+3}$  and  $C_{n+4}$  are not the same polarity.

The ALU data output is routed to several destinations. It can be a data output of the device and it can also be stored in the RAM or the Q register. Eight possible combinations of ALU destination functions are available as defined by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. These combinations are shown in Figure 5.

The four-bit data output field (Y) features three-state outputs and can be directly bus organized. An output control  $(\overline{OE})$  is used to enable the three-state outputs. When  $\overline{OE}$  is HIGH, the Y outputs are in the high-impedance state.

A two-input multiplexer is also used at the data output such that either the A-port of the RAM or the ALU outputs (F) are selected at the device Y outputs. This selection is controlled by the I<sub>6</sub>, I<sub>7</sub>, and I<sub>8</sub> microinstruction inputs. Refer to Figure 12 for the selected output for each microinstruction code combination.

As was discussed previously, the RAM inputs are driven from a three-input multiplexer. This allows the ALU outputs to be entered non-shifted, shifted up one position (X2) or shifted down one position (÷2). The shifter has two ports; one is labeled RAM<sub>0</sub> and the other is labeled RAM<sub>3</sub>. Both of these ports consist of a buffer-driver with a three-state output and an input to the multiplexer. Thus, in the shift up mode, the RAM<sub>3</sub> buffer is enabled and the RAM<sub>0</sub> multiplexer input is enabled. Likewise, in the shift down mode, the RAM<sub>0</sub> buffer and RAM<sub>3</sub> input are enabled. In the no-shift mode, both buffers are in the high-impedance state and the multiplexer inputs are not selected. This shifter is controlled from the I<sub>6</sub>, I<sub>7</sub> and I<sub>8</sub> microinstruction inputs as defined in Figure 5.

Similarly, the Q register is driven from a 3-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q register. In either the shift-up or shift-down mode, the multiplexer selects the Q register data appropriately shifted up or down. The Q shifter also has two ports; one is labeled  $Q_0$  and the other is  $Q_3$ . The operation of these two ports is similar to the RAM shifter and is also controlled from  $I_6$ ,  $I_7$ , and  $I_8$  as shown in Figure 5.

The clock input to the Am2901 controls the RAM, the Q register, and the A and B data latches. When enabled, data is clocked into the Q register on the LOW-to-HIGH transition of the clock. When the clock input is HIGH, the A and B latches are open and will pass whatever data is present at the RAM outputs. When the clock input is LOW, the latches are closed and will retain the last data entered. If the RAM-EN is enabled, new data will be written into the RAM file (word) defined by the B address field when the clock input is LOW.

#### **FUNCTIONAL TABLES**

| Mnemonic |                | MICR           | o cc           | DE            | ALU SO |   |

|----------|----------------|----------------|----------------|---------------|--------|---|

|          | l <sub>2</sub> | l <sub>1</sub> | l <sub>0</sub> | Octal<br>Code | R      | s |

| AQ       | L              | L              | L              | 0             | Α      | Q |

| AB       | L              | L              | н              | 1             | Α      | В |

| ZQ       | L              | н              | L              | 2             | 0      | Q |

| ZB       | L              | н              | н              | 3             | 0      | В |

| ZA       | н              | L              | L              | 4             | 0      | Α |

| DA       | н              | L              | н              | 5             | D      | Α |

| DQ       | Н              | н              | L              | 6             | D      | Q |

| DZ       | н              | н              | н              | 7             | D      | 0 |

|          | N              | IICR | οс | ODE           |                 | SYMBOL |  |

|----------|----------------|------|----|---------------|-----------------|--------|--|

| Mnemonic | l <sub>5</sub> | 14   | lз | Octal<br>Code | ALU<br>Function |        |  |

| ADD      | L              | L    | L  | 0             | R Plus S        | R+S    |  |

| SUBR     | L              | L    | н  | ] 1           | S Minus R       | S-R    |  |

| SUBS     | L              | н    | L  | 2             | R Minus S       | R-S    |  |

| OR       | L              | н    | н  | 3             | RORS            | RvS    |  |

| AND      | н              | L    | L  | 4             | RANDS           | R^S    |  |

| NOTES    | н              | L    | н  | 5             | RANDS           | R∧S    |  |

| EXOR     | н              | н    | L  | 6             | R EX-OR S       | R⊽S    |  |

| EXNOR    | Н              | Н    | н  | 7             | R EX-NOR S      | R₹S    |  |

Figure 3. ALU Source Operand Control.

Figure 4. ALU Function Control.

| Mnemonic | MICRO CODE |    |    | RAM<br>FUNCTION |       | Q-REG.<br>FUNCTION |       | Y      | RAM<br>SHIFTER |                  | Q<br>SHIFTER     |                 |                 |

|----------|------------|----|----|-----------------|-------|--------------------|-------|--------|----------------|------------------|------------------|-----------------|-----------------|

|          | lg         | 17 | 16 | Octal<br>Code   | Shift | Load               | Shift | Load   | OUTPUT         | RAM <sub>0</sub> | RAM <sub>3</sub> | Q <sub>0</sub>  | Q <sub>3</sub>  |

| QREG     | L          | L  | L  | 0               | Х     | NONE               | NONE  | F→Q    | F              | Х                | Х                | X               | X               |

| NOP      | L          | ī  | Н  | 1               | х     | NONE               | Х     | NONE   | F              | Х                | Х                | X               | Х               |

| RAMA     | L          | Н  | L  | 2               | NONE  | F→B                | Х     | NONE   | Α              | Х                | X                | ×               | Х               |

| RAMF     |            | Н  | Н  | 3               | NONE  | F→B                | Х     | NONE   | F              | Х                | X                | X               | х               |

| RAMOD    | н          | ī  | L  | 4               | DOWN  | F/2→B              | DOWN  | Q/2→Q  | F              | F <sub>0</sub>   | IN <sub>3</sub>  | Q <sub>0</sub>  | IN <sub>3</sub> |

| RAMD     | н          | ī  | Н  | 5               | DOWN  | F/2→B              | X     | NONE   | F              | F <sub>0</sub>   | IN <sub>3</sub>  | Q <sub>0</sub>  | Х               |

| RAMQU    | н          | H  | L  | 6               | UP    | 2F → B             | UP    | 2Q → Q | F              | IN <sub>0</sub>  | F <sub>3</sub>   | IN <sub>0</sub> | Q <sub>3</sub>  |

| RAMU     | н          | Н  | Н  | 7               | UP    | 2F → B             | ×     | NONE   | F              | IN <sub>0</sub>  | F <sub>3</sub>   | Х               | Q <sub>3</sub>  |

X = Don't care. Electrically, the shift pin is a TTL input internally connected to a three-state output which is in the high-impedance state. B = Register Addressed by B inputs. UP is toward MSB, DOWN is toward LSB.

Figure 5. ALU Destination Control.

|       |                                | I <sub>210</sub> OCTAL |       |      |       |        |       |       |       |

|-------|--------------------------------|------------------------|-------|------|-------|--------|-------|-------|-------|

|       |                                | 0                      | 1     | 2    | 3     | 4      | 5     | 6     | 7     |

| OCTAL | ALU                            |                        |       |      | ALU S | Source |       |       |       |

| 1543  | Function                       | A,Q                    | A,B   | 0,Q  | 0,B   | O,A    | D,A   | D,Q   | D,0   |

|       | C <sub>n</sub> = L<br>R Plus S | A+Q                    | A + B | a    | В     | Α      | D+A   | D+Q   | D     |

| 0     | R Plus S<br>Cn = H             | A+Q+1                  | A+B+1 | Q+1  | B+1   | A + 1  | D+A+1 | D+Q+1 | D+1   |

|       | C <sub>n</sub> = L             | Q-A-1                  | B-A-1 | Q-1  | B-1   | A-1    | A-D-1 | Q-D-1 | -D-   |

| 1     | S Minus R<br>Cn = H            | Q-A                    | B-A   | a    | В     | A      | A-D   | Q-D   | -D    |

|       | C <sub>n</sub> =L              | A-Q-1                  | A-B-1 | -Q-1 | -B-1  | -A-1   | D-A-1 | D-Q-1 | D - 1 |

| 2     | R Minus S<br>Cn = H            | A-Q                    | A-B   | -Q   | -В    | -A     | D-A   | D-Q   | D     |

| 3     | RORS                           | AvQ                    | AvB   | a    | В     | A      | D√A   | DvQ   | D     |

| 4     | R AND S                        | A^Q                    | A^B   | 0    | 0     | 0      | D^A   | D^Q   | 0     |

| 5     | R AND S                        | Ā∧Q                    | Ā^B   | a    | В     | Α      | D∧A   | Ð∧Q   | 0     |

| 6     | R EX-OR S                      | AVQ                    | A∇B   | Q    | В     | Α.     | DŶA   | DŸQ   | D     |

| 7     | R EX-NOR S                     | ĀVQ                    | Ā₹B   | ō    | B     | Ā      | DVA   | DVQ   | D     |

<sup>+ =</sup> Plus; - = Minus; v = OR; ∧ = AND; ♥ = EX-OR

Figure 6. Source Operand and ALU Function Matrix.

## SOURCE OPERANDS AND ALU FUNCTIONS

There are eight source operand pairs available to the ALU as selected by the  $I_0$ ,  $I_1$ , and  $I_2$  instruction inputs. The ALU can perform eight functions; five logic and three arithmetic. The  $I_3$ ,  $I_4$ , and  $I_5$  instruction inputs control this function selection. The carry input,  $C_{\Pi}$ , also affects the ALU results when in the arithmetic mode. The  $C_{\Pi}$  input has no effect in the logic mode. When  $I_0$  through  $I_5$  and  $C_{\Pi}$  are viewed together, the matrix of

Figure 6 results. This matrix fully defines the ALU/source operand function for each state.

The ALU functions can also be examined on a "task" basis, i.e., add, subtract, AND, OR, etc. In the arithmetic mode, the carry will affect the function performed while in the logic mode, the carry will have no bearing on the ALU output. Figure 7 defines the various logic operations that the Am2901 can perform and Figure 8 shows the arithmetic functions of the device. Both carry-in LOW ( $C_{\rm n}=0$ ) and carry-in HIGH ( $C_{\rm n}=1$ ) are defined in these operations.

|                                              | ·        |                          |

|----------------------------------------------|----------|--------------------------|

| Octal<br>1 <sub>543</sub> , 1 <sub>210</sub> | Group    | Function                 |

| 4 0<br>4 1<br>4 5<br>4 6                     | AND      | A^Q<br>A^B<br>D^A<br>D^Q |

| 3 0<br>3 1<br>3 5<br>3 6                     | OR       | AVQ<br>AVB<br>DVA<br>DVQ |

| 6 0<br>6 1<br>6 5<br>6 6                     | EX-OR    | AVQ<br>AVB<br>DVA<br>DVQ |

| 7 0<br>7 1<br>7 5<br>7 6                     | EX-NOR   | AVQ<br>AVB<br>DVA<br>DVQ |

| 7 2<br>7 3<br>7 4<br>7 7                     | INVERT   | ©<br>B<br>A<br>D         |

| 6 2<br>6 3<br>6 4<br>6 7                     | PASS     | Q<br>B<br>A<br>D         |

| 3 2<br>3 3<br>3 4<br>3 7                     | PASS     | Q<br>B<br>A<br>D         |

| 4 2<br>4 3<br>4 4<br>4 7                     | ''ZERO'' | 0<br>0<br>0              |

| 5 0<br>5 1<br>5 5<br>5 6                     | MASK     | Ā^Q<br>Ā^B<br>D^A<br>D^Q |

| Octal                                                | C <sub>n</sub> =       | · L                                                                  | C <sub>n</sub> =H      |                                               |  |

|------------------------------------------------------|------------------------|----------------------------------------------------------------------|------------------------|-----------------------------------------------|--|

| l <sub>543</sub> ,<br>l <sub>210</sub>               | Group                  | Function                                                             | Group                  | Function                                      |  |

| 0 0<br>0 1<br>0 5<br>0 6                             | ADD                    | A+Q<br>A+B<br>D+A<br>D+Q                                             | ADD plus<br>one        | A+Q+1<br>A+B+1<br>D+A+1<br>D+Q+1              |  |

| 0 2<br>0 3<br>0 4<br>0 7                             | PASS                   | Q<br>B<br>A<br>D                                                     | Increment              | Q+1<br>B+1<br>A+1<br>D+1                      |  |

| 1 2<br>1 3<br>1 4<br>2 7                             | Decrement              | Q-1<br>B-1<br>A-1<br>D-1                                             | PASS                   | Q<br>B<br>A<br>D                              |  |

| 2 2<br>2 3<br>2 4<br>1 7                             | 1's Comp.              | -Q-1<br>-B-1<br>-A-1<br>-D-1                                         | 2's Comp.<br>(Negate)  | -Q<br>-B<br>-A<br>-D                          |  |

| 1 0<br>1 1<br>1 5<br>1 6<br>2 0<br>2 1<br>2 5<br>2 6 | Subtract<br>(1's Comp) | Q-A-1<br>B-A-1<br>A-D-1<br>Q-D-1<br>A-Q-1<br>A-B-1<br>D-A-1<br>D-Q-1 | Subtract<br>(2's Comp) | Q-A<br>B-A<br>A-D<br>Q-D<br>A-Q<br>A-B<br>D-A |  |

Figure 7. ALU Logic Mode Functions.

Figure 8. ALU Arithmetic Mode Functions.

## LOGIC FUNCTIONS FOR G, P, Cn + 4, AND OVR

The four signals G, P,  $C_{n+4}$ , and OVR are designed to indicate carry and overflow conditions when the Am2901 is in the add or subtract mode. The table below indicates the logic equations for these four signals for each of the eight ALU functions. The R and S inputs are the two inputs selected according to Figure 3.

#### Definitions (+ = OR)

$$P_0 = R_0 + S_0 \qquad G_0 = R_0S_0$$

$$P_1 = R_1 + S_1 \qquad G_1 = R_1S_1$$

$$P_2 = R_2 + S_2 \qquad G_2 = R_2S_2$$

$$P_3 = R_3 + S_3 \qquad G_3 = R_3S_3$$

$$C_4 = G_3 + P_3G_2 + P_3P_2G_1$$

$$+ P_3P_2P_1G_0 + P_3P_2P_1P_0C_n$$

$$C_3 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_n$$

| 1543 | Function | P                                                                 | Ğ                                                                                                                                                           | Cn+4                                                                                                     | OVR                                                                          |

|------|----------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 0    | R+S      | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>       | G <sub>3</sub> + P <sub>3</sub> G <sub>2</sub> + P <sub>3</sub> P <sub>2</sub> G <sub>1</sub> + P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> G <sub>0</sub> | C <sub>4</sub>                                                                                           | C <sub>3</sub> ∇C <sub>4</sub>                                               |

| 1    | S-R      | <u> </u>                                                          | Same as R + S equations, but substitute                                                                                                                     | Ri for Ri in definitions                                                                                 |                                                                              |

| 2    | R-S      | <b>—</b>                                                          | Same as R + S equations, but substitute                                                                                                                     | Si for Si in definitions                                                                                 |                                                                              |

| 3    | RvS      | LOW                                                               | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>                                                                                                 | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> + C <sub>n</sub>                             | P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> + C <sub>n</sub> |

| 4    | R^S      | LOW                                                               | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub>                                                                                           | G3 + G2 + G1 + G0 + Cn                                                                                   | G3 + G2 + G1 + G0 + Cn                                                       |

| 5    | Ā∧S      | LOW                                                               | Same as R^S equations,                                                                                                                                      | but substitute $\overline{R_i}$ for $R_i$ in de                                                          | finitions                                                                    |

| 6    | R₹S      | · · · · · · · · · · · · · · · · · · ·                             | Same as RVS, but substitute Ri fo                                                                                                                           | or R <sub>i</sub> in definitions————                                                                     |                                                                              |

| 7    | FIVS     | G <sub>3</sub> + G <sub>2</sub> + G <sub>1</sub> + G <sub>0</sub> | G <sub>3</sub> + P <sub>3</sub> G <sub>2</sub> + P <sub>3</sub> P <sub>2</sub> G <sub>1</sub> + P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> | $\frac{\overline{G_3} + P_3\overline{G_2} + P_3P_2\overline{G_1}}{+ P_3P_2P_1P_0(G_0 + \overline{C}_n)}$ | See note                                                                     |

Note:  $[P_2 + G_2P_1 + G_2G_1P_0 + G_2G_1G_0C_n]$   $\forall$  $[P_3 + G_3P_2 + G_3G_2P_1 + G_3G_2G_1P_0 + G_3G_2G_1G_0C_n]$  + = OR

Figure 9.

#### MINIMUM CYCLE TIME CALCULATIONS FOR 16-BIT SYSTEMS

Speeds used in calculations for parts other than Am2901C are representative for available MSI parts.

AF001621

#### Pipelined System. Add without Simultaneous Shift.

|                                               | DATA LOOP                                                                                                                                            |                     | С                                          | ONTROL LOOP                                                        |                     |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------|--------------------------------------------------------------------|---------------------|

| ①Register<br>+ ②2901C<br>+ ③2902A<br>+ ④2901C | Clock to Output A, B to G, P G <sub>0</sub> , P <sub>0</sub> to C <sub>n+z</sub> C <sub>n</sub> to C <sub>n+4</sub> , OVR, F <sub>3</sub> , F = 0, Y | 9<br>37<br>7<br>25  | ①Register<br>+ @MUX<br>+ ⑦2910A<br>+ @PROM | Clock to Output<br>Select to Output<br>CC to Output<br>Access Time | 9<br>13<br>30<br>40 |

| + ⑤Register                                   | Setup Time                                                                                                                                           | 80ns<br>Minimum clo | + ①Register  ck period = 94ns              | Setup Time                                                         | 94ns                |

### Pipelined System. Simultaneous Add and Shift Down.

| D/                                                                          | ATA LOOP                                                                                                                                                  |                                                          | C                                                         | ONTROL LOOP                                                                      |                                  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------|

| ①Register<br>+ ②2901C<br>+ ③2902A<br>+ ④2901C<br>+ ⑤XOR and MUX<br>+ ⑥2901C | Clock to Output<br>A, B to G,P<br>G <sub>0</sub> , P <sub>0</sub> to C <sub>n+z</sub><br>C <sub>n</sub> to F <sub>3</sub> , OVR<br>RAM <sub>3</sub> Setup | 9<br>37<br>7<br>22<br>21<br>12<br>109ns<br>Minimum clock | ①Register<br>+ ⑥MUX<br>+ ②2910A<br>+ ⑥PROM<br>+ ①Register | Clock to Output<br>Select to Output<br>CC to Output<br>Access Time<br>Setup Time | 9<br>13<br>30<br>40<br>2<br>94ns |

Figure 10.

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65°C to +150°C             |

|-----------------------------------------------|

| Ambient Temperature Under Bias55°C to +125°C  |

| Supply Voltage to Ground Potential            |

| Continuous0.5V to +7.0V                       |

| DC Voltage Applied to Outputs For             |

| High Output State0.5V to +V <sub>CC</sub> max |

| DC Input Voltage0.5V to +5.5V                 |

| DC Output Current, Into Outputs               |

| DC Input Current                              |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices               |                          |

|--------------------------------------|--------------------------|

| Temperature                          | 0°C to +70°C             |

| Supply Voltage                       | + 4.75V to + 5.25V       |

| Military (M) Devices                 |                          |

| Temperature                          | 55°C to +125°C           |

| Supply Voltage                       | +4.5V to +5.5V           |

| Operating ranges define those limits | over which the function- |

| ality of the device is guaranteed.   |                          |

#### DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters              | Description                                                   |                                                                | Test Conditions (Note 1)                                          |                                                                                             | Min | Max      | Unite |

|-------------------------|---------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|----------|-------|

|                         |                                                               |                                                                |                                                                   | I <sub>OH</sub> = -1.6mA<br>Y <sub>0</sub> Y <sub>1</sub> , Y <sub>2</sub> , Y <sub>3</sub> | 2.4 |          |       |

|                         |                                                               |                                                                |                                                                   | IOH = -1.0mA, Cn + 4                                                                        | 2.4 |          | 1     |

|                         |                                                               | IOU = -800 MA OVR D                                            |                                                                   | I <sub>OH</sub> = -800μA, OVR, P                                                            | 2.4 | <b>-</b> | 1     |

| VOH Output HIGH Voltage | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or | VII                                                            | I <sub>OH</sub> = -600μA, F <sub>3</sub>                          | 2.4                                                                                         |     | Volts    |       |

|                         |                                                               | 1 114 1111 1                                                   | - 12                                                              | I <sub>OH</sub> = -600μA<br>RAM <sub>0</sub> , 3, Q <sub>0,3</sub>                          | 2.4 |          |       |

|                         |                                                               |                                                                |                                                                   | I <sub>OH</sub> = -1.6mA, G                                                                 | 2.4 |          |       |

| ICEX                    | Output Leakage Current<br>For F = 0 Output                    | V <sub>CC</sub> = MIN,<br>V <sub>IN</sub> = V <sub>IH</sub> or |                                                                   | 101                                                                                         |     | 250      | μΑ    |

|                         |                                                               | + **                                                           |                                                                   | IOL = 20mA (COM'L) (Note 4)                                                                 |     | 0.5      |       |

|                         |                                                               |                                                                | Y <sub>0</sub> , Y <sub>1</sub> , Y <sub>2</sub> , Y <sub>3</sub> | I <sub>OL</sub> = 16mA (MIL) (Note 4)                                                       |     | 0.5      | 1     |

|                         |                                                               | V <sub>CC</sub> = MIN,                                         | G, F = 0                                                          | I <sub>OL</sub> = 16mA                                                                      |     | 0.5      |       |

| VOL                     | Output LOW Voltage                                            | VIN = VIH                                                      | Cn + 4                                                            | I <sub>OL</sub> = 10mA                                                                      |     | 0.5      | 1     |

| ·OL                     |                                                               | or VIL                                                         | OVR, P                                                            | I <sub>OL</sub> = 8.0mA                                                                     |     | 0.5      |       |

|                         |                                                               |                                                                | F <sub>3</sub> , RAM <sub>0, 3</sub> ,<br>Q <sub>0,3</sub>        | I <sub>OL</sub> = 6.0mA                                                                     |     | 0.5      | ]     |

| VIH                     | Input HIGH Level                                              | Guaranteed input logical HIGH voltage for all inputs (Note 6)  |                                                                   |                                                                                             | 2.0 |          | Volt  |

| VIL                     | Input LOW Level                                               | Guaranteed input logical LOW voltage for all inputs (Note 6)   |                                                                   |                                                                                             | 0.8 | Volt     |       |

| VI                      | Input Clamp Voltage                                           | V <sub>CC</sub> = MIN,                                         | I <sub>IN</sub> = - 18mA                                          |                                                                                             |     | -1.5     | Volt  |

| <del> </del>            |                                                               |                                                                |                                                                   | Clock, OE                                                                                   |     | -0.36    | ]     |

|                         |                                                               |                                                                |                                                                   | A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub>                           |     | -0.36    | ]     |

|                         |                                                               |                                                                |                                                                   | B <sub>0</sub> , B <sub>1</sub> , B <sub>2</sub> , B <sub>3</sub>                           |     | -0.36    | ]     |

|                         |                                                               |                                                                |                                                                   | D <sub>0</sub> , D <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub>                           |     | -0.72    |       |

| I <sub>IL</sub>         | Input LOW Current                                             | V <sub>CC</sub> = MAX,                                         | $V_{IN} = 0.5V$                                                   | 10, 11, 12, 16, 18                                                                          |     | -0.36    | mA    |

|                         |                                                               | i                                                              |                                                                   | 13, 14, 15, 17                                                                              |     | -0.72    |       |

|                         |                                                               |                                                                | RAM <sub>0, 3</sub> , Q <sub>0,3</sub> (Note 3)                   |                                                                                             |     | -0.8     | _     |

|                         |                                                               |                                                                |                                                                   | C <sub>n</sub>                                                                              |     | -3.6     |       |

|                         |                                                               |                                                                |                                                                   | Clock, OE                                                                                   |     | 20       |       |

|                         |                                                               |                                                                |                                                                   | A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> , A <sub>3</sub>                           |     | 20       |       |

|                         |                                                               | 1                                                              |                                                                   | B <sub>0</sub> , B <sub>1</sub> , B <sub>2</sub> , B <sub>3</sub>                           |     | 20       |       |

|                         |                                                               |                                                                |                                                                   | D <sub>0</sub> , D <sub>1</sub> , D <sub>2</sub> , D <sub>3</sub>                           |     | 40       | μА    |

| lıн                     | Input HIGH Current                                            | V <sub>CC</sub> = MAX,                                         | $V_{IN} = 2.7V$                                                   | 10, 11, 12, 16, 18                                                                          |     | 20       |       |

|                         |                                                               |                                                                | 13, 14, 15, 17                                                    |                                                                                             | 40  |          |       |

|                         |                                                               |                                                                |                                                                   | RAM <sub>0, 3</sub> , Q <sub>0,3</sub> (Note 3)                                             |     | 100      | _     |

|                         |                                                               |                                                                |                                                                   | Cn                                                                                          |     | 200      | 1     |

| Parameters                                     | Description                  | Test Conditions (Note 1)                                                                                                   |                                                                       |                                   |                                          | Min | Max | Units |

|------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------|------------------------------------------|-----|-----|-------|

| lı .                                           | Input HIGH Current           | V <sub>CC</sub> = MAX,                                                                                                     | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 5.5V                         |                                   |                                          |     | 1.0 | mA    |

|                                                |                              |                                                                                                                            |                                                                       | Yn. Y1.                           | V <sub>O</sub> = 2.4V                    |     | 50  |       |

| IOZH Off State (High Impedance) Output Current | İ                            |                                                                                                                            | Y <sub>0</sub> , Y <sub>1</sub> ,<br>Y <sub>2</sub> , Y <sub>3</sub>  | V <sub>O</sub> = 0.5V             |                                          | -50 | ]   |       |

|                                                | V <sub>CC</sub> = MAX        |                                                                                                                            | RAM <sub>0. 3</sub>                                                   | V <sub>O</sub> = 2.4V<br>(Note 3) |                                          | 100 | μΑ  |       |

|                                                |                              | Q <sub>0</sub> , 3                                                                                                         | V <sub>O</sub> = 0.5V<br>(Note 3)                                     |                                   | -800                                     |     |     |       |

|                                                |                              | <del> </del>                                                                                                               | Y <sub>0</sub> , Y <sub>1</sub> , Y <sub>2</sub> , Y <sub>3</sub> , G |                                   | -30                                      | -85 |     |       |

|                                                |                              | $V_{CC} = MAX + 0.5V, V_O = 0.5V$ $\begin{array}{c} C_{n+4} \\ OVR, \overline{P} \\ F_3 \\ RAM_{0.3}, Q_{0.3} \end{array}$ |                                                                       |                                   | -30                                      | -85 |     |       |

| los                                            | Output Short Circuit Current |                                                                                                                            |                                                                       | OVR, P                            |                                          | -30 | -85 | mA    |

| .03                                            | (Note 2)                     |                                                                                                                            |                                                                       | F <sub>3</sub>                    |                                          | -30 | -85 |       |

|                                                |                              |                                                                                                                            |                                                                       | FIAM <sub>0, 3</sub> ,            | FIAM <sub>0, 3</sub> , Q <sub>0, 3</sub> |     | -85 |       |

|                                                |                              | <u> </u>                                                                                                                   | COM'L Only                                                            | TA = 0°C 1                        | to +70°C                                 |     | 265 |       |

| Power Supply Current (Note 5)                  | D O O                        | .                                                                                                                          | (Note 4)                                                              | $T_A = +70^{\circ}$               | С                                        |     | 220 | ]     |

|                                                | (Note 5)                     | V <sub>CC</sub> = MAX                                                                                                      | MIL Only                                                              | T <sub>C</sub> = -55°             | C to+125°C                               |     | 280 | mA    |

|                                                | , ,                          | (Note 4)                                                                                                                   |                                                                       | T <sub>C</sub> = + 125            | 5°C                                      |     | 198 |       |

#### Note:

- tex.

1. V<sub>CC</sub> conditions shown as MIN or MAX, refer to the military (±10%) or commercial (±5%) V<sub>CC</sub> limits.

2. Not more than one output should be stored at a time. Duration of the short circuit test should not exceed one second.

3. These are three-state outputs internally connected to TTL inputs. Input characteristics are measured with lens in a state such that the three-state output is OFF.

4. "MIL" = Am2901CXM, DM, FM, LM, "COM'L" = Am2901CXC, PC, DC, LC.

5. Worst case I<sub>CC</sub> is measured at the lowest temperature in the specified operating range.

6. These input levels provide zero noise immunity and should only be static tested in a noise-free environment, (not functionally tested).

#### I. Am2901B Guaranteed Commercial Range Performance

The tables below specify the guaranteed performance of the Am2901B over the commercial operating range of 0°C to +70°C, with VCC from 4.75V to 5.25V. All data are in ns. with inputs switching between 0V and 3V at 1V/ns and measurements made at 1.5V. All outputs have maximum DC load.

This data applies to the following part numbers: Am2901BPC Am2901BDC

#### A. Cycle Time and Clock Characteristics.

| Read-Modify-Write Cycle (from selection of A, B registers to end of cycle.) | 69ns  |

|-----------------------------------------------------------------------------|-------|

| Maximum Clock Frequency to shift Q (50% duty cycle. I = 432 or 632)         | 16MHz |

| Minimum Clock LOW Time                                                      | 30ns  |

| Minimum Clock HIGH Time                                                     | 30ns  |

| Minimum Clock Period                                                        | 69ns  |

#### B. Combinational Propagation Delays. (Note 1) $C_L = 50pF$

|                           |    | To Output |      |      |       |     |              |          |

|---------------------------|----|-----------|------|------|-------|-----|--------------|----------|

| From Input                | Υ  | F3        | Cn+4 | G, P | F = 0 | OVR | RAM0<br>RAM3 | Q0<br>Q3 |

| A, B Address              | 60 | 61        | 59   | 50   | 70    | 67  | 71           | -        |

| D .                       | 38 | 36        | 40   | 33   | 48    | 44  | 45           | -        |

| Cn                        | 30 | 29        | 20   | -    | 37    | 29  | 38           | -        |

| 1012                      | 50 | 47        | 45   | 45   | 56    | 53  | 57           | -        |

| 1345                      | 51 | 52        | 52   | 45   | 60    | 49  | 53           | -        |

| 1678                      | 28 | -         | -    | -    | -     | _   | 35           | 35       |

| A Bypass ALU<br>(I = 2XX) | 37 | _         | -    | -    | -     | -   | -            | -        |

| Clock                     | 49 | 48        | 47   | 37   | 58    | 55  | 59           | 29       |

#### C. Set-up and Hold Times Relative to Clock (CP) Input. (Note 1)

|                          | CP:                        | <u> </u>                | L                           |                          |

|--------------------------|----------------------------|-------------------------|-----------------------------|--------------------------|

| Input                    | Set-up Time<br>Before H →L | Hold Time<br>After H →L | Set-up Time<br>Before L → H | Hold Time<br>After L → H |

| A, B Source Address      | 20                         | 0 (Note 3)              | 69 (Note 4)                 | 0                        |

| B Destination<br>Address | 15                         | Do Not Cha              | ange (Note 2)               | 0                        |

| D                        | _                          | _                       | 51                          | 0                        |

| Cn                       | -                          | -                       | 39                          | 0                        |

| 1012                     | _                          | _                       | 56                          | 0                        |

| 1345                     | -                          | -                       | 55                          | 0                        |

| 1678                     | 11                         | Do Not Cha              | inge (Note 2)               | 0                        |

| RAMO, 3, QO, 3           | -                          | _                       | 16                          | 0                        |

#### D. Output Enable/Disable Times.

Output disable tests performed with Ci = 5pF and measured to 0.5V change of output voltage level.

| Input | Output | Enable | Disable |

|-------|--------|--------|---------|

| ŌĒ    | Y      | 35     | 25      |

- NOTES: 1. A dash indicates a propagation delay path or set-up time constraint does not exist.

2. Certain signals must be stable during the entire clock LOW time to avoid erroneous operation. This is indicated by the phrase "do not change".

- a Source addresses must be stable prior to the clock H<sup>-</sup>L transition to allow time to access the source data before the latches close. The A address may then be changed. The B address could be changed if it is not a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock LOW time.

- 4. The set-up time prior to the clock L→H transition is to allow time for data to be accessed, passed through the ALU, and returned to the RAM. It indicates all the time from stable A and B addresses to the clock L-H transition, regardless of when the clock H-L transition occurs.

#### II. Am2901B Guaranteed Military Range **Performance**

The tables below specify the guaranteed performance of the Am2901B over the military operating range of -55°C to +125°C, with V<sub>CC</sub> from 4.5V to 5.5V. All data are in ns, with inputs switching between 0V and 3V at 1V/ns and measurements made at 1.5V. All outputs have maximum DC load.

This data applies to the following part numbers: Am2901BDM Am2901BFM

## A. Cycle Time and Clock Characteristics.

| Read-Modify-Write Cycle (from selection of A, B registers to end of cycle.) | 88ns  |

|-----------------------------------------------------------------------------|-------|

| Maximum Clock Frequency to shift Q (50% duty cycle. I = 432 or 632)         | 15MHz |

| Minimum Clock LOW Time                                                      | 30ns  |

| Minimum Clock HIGH Time                                                     | 30ns  |

| Minimum Clock Period                                                        | 88ns  |

#### B. Combinational Propagation Delays. (Note 1) $C_L = 50pF$

| •                      | To Output |    |      |      |       |     |              |          |

|------------------------|-----------|----|------|------|-------|-----|--------------|----------|

| From Input             | Y         | F3 | Cn+4 | G, P | F = 0 | OVR | RAM0<br>RAM3 | Q0<br>Q3 |

| A, B Address           | 82        | 84 | 80   | 70   | 90    | 86  | 94           |          |

| D                      | 44        | 38 | 40   | 34   | 50    | 45  | 48           | _        |

| Cn                     | 34        | 32 | 24   | _    | 38    | 31  | 39           |          |

| 1012                   | 53        | 50 | 47   | 46   | 65    | 55  | 58           |          |

| 1345                   | 58        | 58 | 58   | 48   | 64    | 56  | 55           | _        |

| 1678                   | 29        | _  | -    | -    | -     |     | 27           | 27       |

| A Bypass ALU (I = 2XX) | 50        | -  | -    | -    | _     | -   | -            |          |

| Clock _                | 53        | 50 | 49   | 41   | 63    | 58  | 61           | 31       |

## C. Set-up and Hold Times Relative to Clock (CP) Input. (Note 1)

|                          | CP:                         | <u> </u>                 | └ <i>┈</i>                 |                          |

|--------------------------|-----------------------------|--------------------------|----------------------------|--------------------------|

| Input                    | Set-up Time<br>Before H → L | Hold Time<br>After H → L | Set-up Time<br>Before L →H | Hold Time<br>After L → H |

| A, B Source Address      | 30                          | 0 (Note 3)               | 88 (Note 4)                | 0                        |

| B Destination<br>Address | 15                          | Do Not Cha               | ange (Note 2)              | 0                        |

| D                        | -                           | -                        | 55                         | 0                        |

| Cn                       | -                           | -                        | 42                         | 0                        |

| 1012                     | _                           | -                        | 58                         | 0                        |

| 1345                     | _                           | -                        | 62                         | 0                        |

| 1678                     | 14                          | Do Not Cha               | ange (Note 2)              | 0                        |

| RAMO, 3, Q0, 3           |                             | _                        | 18                         | 3                        |

#### D. Output Enable/Disable Times.

Output disable tests performed with CL = 5pF and measured to 0.5V change of output voltage level.

| Input | Output | Enable | Disable |

|-------|--------|--------|---------|

| ŌĒ    | Y      | 40     | 25      |

NOTES: 1. A dash indicates a propagation delay path or set-up time constraint does not exist.

2. Certain signals must be stable during the entire clock LOW time to avoid erroneous operation. This is indicated by

the phrase "do not change"

- 3. Source addresses must be stable prior to the clock H-L transition to allow time to access the source data before the latches close. The A address may then be changed. The B address could be changed if it is not a destination: i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock LOW

- 4. The set-up time prior to the clock L¬H transition is to allow time for data to be accessed, passed through the ALU, and returned to the RAM. It includes all the time from stable A and B addresses to the clock L¬H transition, regardless of when the clock H-L transition occurs.

#### III. Am2901C Guaranteed Commercial Range Performance

The tables below specify the guaranteed performance of the Am2901C over the commercial operating range of 0°C to +70°C, with V<sub>CC</sub> from 4.75V to 5.25V. All data are in ns, with inputs switching between 0V and 3V at 1V/ns and measurements made at 1.5V. All outputs have maximum DC load.

This data applies to the following part numbers: Am 2901 CPC Am2901CDC Am2901CLC

### A. Cycle Time and Clock Characteristics.

| Read-Modify-Write Cycle (from selection of A, B registers to end of cycle.) | 31ns  |

|-----------------------------------------------------------------------------|-------|

| Maximum Clock Frequency to shift Q (50% duty cycle, I = 432 or 632)         | 32MHz |

| Minimum Clock LOW Time                                                      | 15ns  |

| Minimum Clock HIGH Time                                                     | 15ns  |

| Minimum Clock Period                                                        | 31ns  |

#### B. Combinational Propagation Delays, (Note 1) $C_L = 50pF$

|                        |    | To Output |      |      |       |     |              |          |

|------------------------|----|-----------|------|------|-------|-----|--------------|----------|

| From Input             | Υ  | F3        | Cn+4 | G, P | F = 0 | OVR | RAMO<br>RAM3 | Q0<br>Q3 |

| A, B Address           | 40 | 40        | 40   | 37   | 40    | 40  | 40           | -        |

| D                      | 30 | 30        | 30   | 30   | 38    | 30  | 30           | -        |

| Cn                     | 22 | 22        | 20   | -    | 25    | 22  | 25           | _        |

| 1012                   | 35 | 35        | 35   | 37   | 37    | 35  | 35           | -        |

| 1345                   | 35 | 35        | 35   | 35   | 38    | 35  | 35           | -        |

| 1678                   | 25 | -         | -    | -    | -     | -   | 26           | 26       |

| A Bypass ALU (i = 2XX) | 35 | -         | _    | _    | -     | -   | -            | -        |

| Clock _                | 35 | 35        | 35   | 35   | 35    | 35  | 35           | 28       |

#### C. Set-up and Hold Times Relative to Clock (CP) Input. (Note 1)

| Input                    | CP:                        |                         |                             |                          |

|--------------------------|----------------------------|-------------------------|-----------------------------|--------------------------|

|                          | Set-up Time<br>Before H →L | Hold Time<br>After H →L | Set-up Time<br>Before L → H | Hold Time<br>After L → H |

| A, B Source Address      | 15                         | 1 (Note 3)              | 30, 15 + Tpwt<br>(Note 4)   | . 1                      |

| B Destination<br>Address | 15                         | Do Not Change (Note 2)  |                             | 1                        |

| D                        | -                          | -                       | 25                          | 0                        |

| Cn                       | -                          | -                       | 20                          | 0                        |

| 1012                     | -                          | _                       | 30                          | 0                        |

| 1345                     | -                          | _                       | 30                          | 0                        |

| 1678                     | 10                         | Do Not Cha              | inge (Note 2)               | 0                        |

| PAM0, 3, Q0, 3           | -                          | -                       | 12                          | 0                        |

#### D. Output Enable/Disable Times.

Output disable tests performed with C1 = 5pF and measured to 0.5V change of output voltage level.

| Input | Output | Enable | Disable |

|-------|--------|--------|---------|